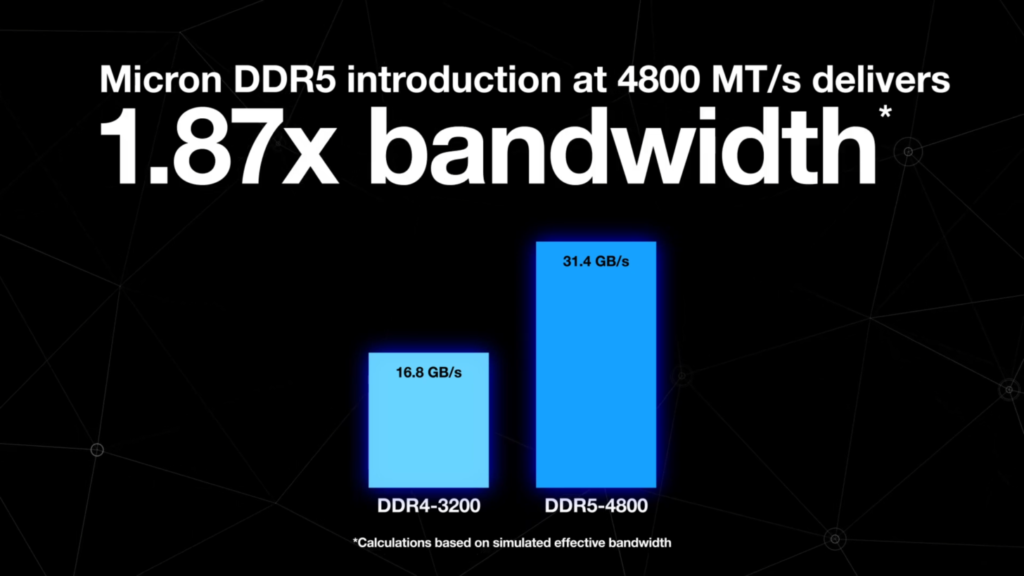

The bulk shipping of DDR5 SDRAM memory for the data centre that is certified for the newest AMD EPYC 9004 Series processors was announced by Micron Technology, Inc. In comparison to DDR4 3200, Micron’s new DDR5 SDRAM offers 1.5 times the data rates at 4800 MT/s and allows features like on-die ECC, Error Check and Scrub (ECS), and fault bounds for greater data centre dependability while continuing to boost density.

Furthermore, Micron offers adaptable memory solutions that can support the ongoing increase of CPU cores for data-intensive workloads like AI, advanced analytics, and high-performance computing (HPC).

Micron DDR5 memory, which has start data rates of 4800 MT/s and additional features to enhance overall data bus efficiency, enables a 36% increase in bus efficiency and roughly twice the effective bandwidth when compared to DDR4 3200 to support the continued expansion of CPU cores in the modern data centre.

As processors and workloads continue to advance, Micron will continue to develop DDR5 to support data rates up to 8800 MT/s, which would provide three times the effective bandwidth compared to DDR4 3200.

There has never been a greater need for systems that can give better computational capability. The memory bandwidth per CPU core has been declining as CPUs in contemporary servers house more computational units. This is lessened by DDR5 memory, which offers the fastest bandwidth of any DDR generation. DDR5 is an advancement over earlier generations in that it provides greater bandwidths, as well as greater scalability, dependability, and availability.

Micron was one of the first companies to test DDR5 with customers in data centres and has been a key contributor to JEDEC’s development of the DDR5 memory specifications since the project’s start. System designers were given early access to crucial internal resources to help with their DDR5 certification and qualification processes through the unique Micron Technology Enablement Program (TEP). Collaboration efforts are also going strong as we engage with system enablers to expand DDR5 RAS features, data speeds, and the total feature set that is currently accessible.

Also read: