Yesterday, Marvell announced the industry’s first 112G 5nm SerDes solution. In the market, there are three SoCs, built on TSMC’s N5 process: the Apple A14 SoC, used in iPhone 12 series, the Apple M1 SoC, used in Mac Mini and MBA/MBP, and the Huawei Kirin 9000 5G SoC, used in the Mate 40 Pro.

Here comes the next one in the list, but it is not the standard SoCs. It has an IP block, which converts parallel data into serial data. SerDes IPs are used to get high-speed communication between chips.

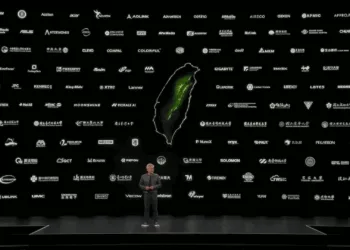

Marvell is a powerful foundation, trusted by leading technology companies of the world for 25 years. The company builds semiconductor solutions to secure, store, and move data according to its customers’ needs.

All the latest chip-to-chip networking infrastructure is depending upon the high-speed SerDes connections. The high-speed connection is presently a 56G connection; now, with 112G, it will double the speed. Many companies have 112G IP available, but Marvell is the first who implies it in 5nm and propose it for licensing.

The new 112G SerDes have an aim to offer a less power consuming solution with a lower potential error rate for those high-speed and high-reliability infrastructure applications. Marvell is claiming a remarkable power reduction in energy when a bit is transferred. The reading says less than 40dB insertion loss is seen when at 112G PAM4 channels were operated.

Sandeep Bharathi, Marvell’s senior vice president of Central Engineering, said that “Our new 112G 5nm SerDes solution, with its industry-leading power, performance and area metrics is a true game-changer and will help scale data infrastructure to meet growing interconnect requirements. System performance is typically limited by bandwidth and power in most infrastructure applications, and our new 112G solution in 5nm addresses this by doubling the bandwidth while reducing the overall I/O power.”

For the implementation of 112G, Marvell is already working with its custom ASIC customers covering multiple markets.

Do check out: