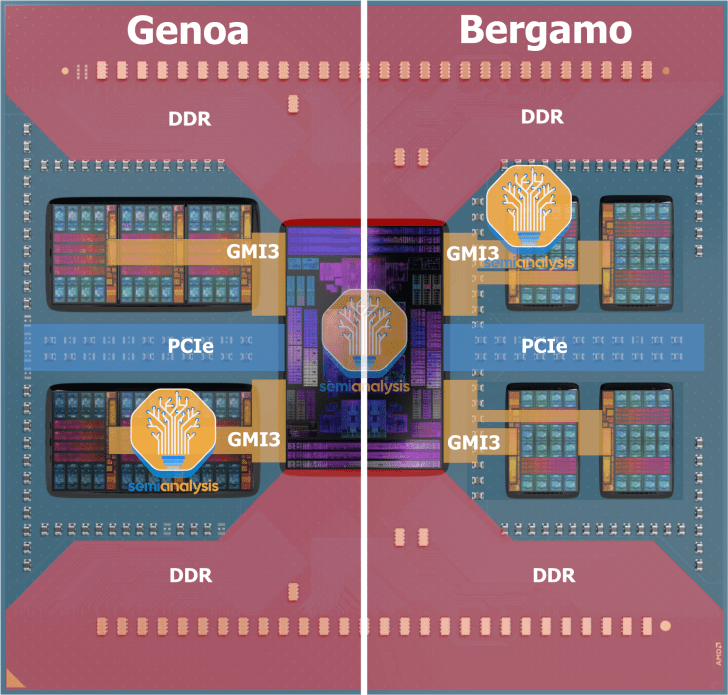

Semianalysis has disclosed further information about AMD’s future EPYC Bergamo CPUs, which will be powered by the new Zen 4C Dense cores. The AMD EPYC Bergamo CPU range is set to debut next week at the “AMD Data Centre and AI Technology Premiere,” during which the firm will discuss its server, cloud, and AI product families.

AMD’s EPYC Bergamo CPU chips may seem similar since they are part of the same EPYC 9004 family, but inside their hearts, they are very different beast that targets a very unique set of applications.

The biggest opponent for AMD’s EPYC Bergamo CPU is Intel’s numerous Arm & compute-density optimised processors, such as Sierra Forest, which will include up to 144 E-Cores. If all goes according to plan with Intel 4, Intel’s solution will not be available until the first half of 2024.

This will also compete with NVIDIA’s Grace, which is based entirely on Arm cores, and a slew of other Arm-based chips that are becoming commonplace in large tech data centres.

AMD’s EPYC Bergamo CPU will have up to 128 cores based on Zen 4C cores manufactured on TSMC’s 4nm manufacturing node, which is a little improvement above the 5nm production node that currently powers the Zen 4 cores.

It will handle up to 256 threads, although Intel’s E-Cores do not, it will support 12-channel DDR5 memory, PCIe Gen 5.0 functionality, and it will be drop-in compatible with the existing SP5 socket with no software port required because the same Zen 4 ISA is used.

However, Dylan Patel of Semianalysis takes a deeper look into the architectural side of things and reveals specifications for two of the CPUs that will be released this month, the EPYC 9754 with 128 cores and the EPYC 9734 with 112 cores.

The specifications are nearly identical to what was previously released, but the clock speeds have been modified due to the difference between ES clocks from a year ago and retail clocks from now.

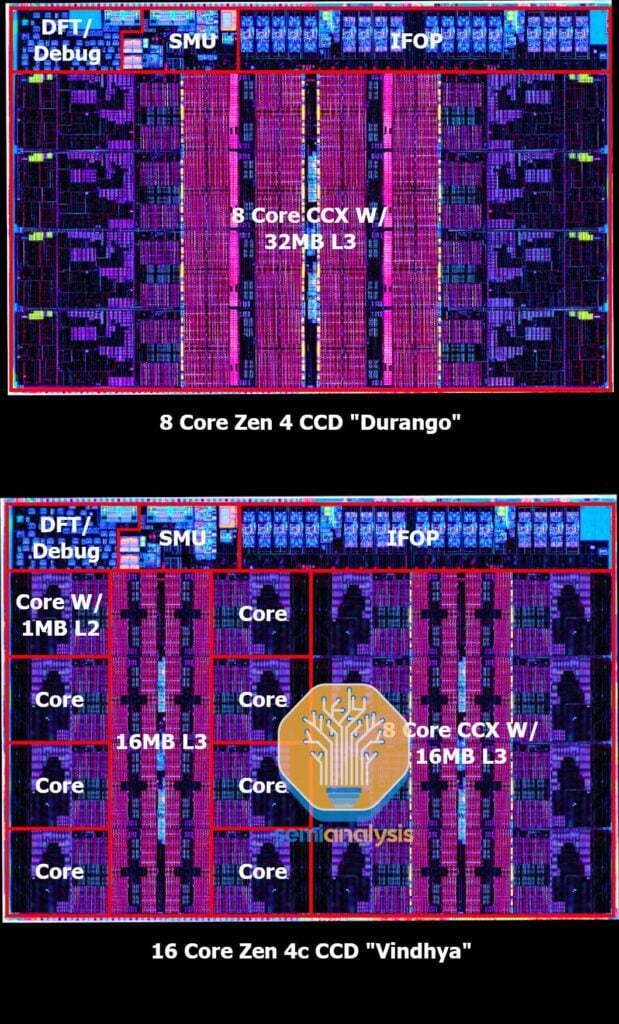

According to reports, the EPYC Bergamo CPU chips feature eight Zen 4C CCDs with up to 16 Zen 4C CPUs. Each CCD is made up of two CCXs, each with eight cores and a shared 16 MB L3 cache.

As a result, the dual-CCX portioning for Zen 4C has returned, as opposed to the single unified CCD/CCX portioning observed from Zen 3.

AMD was able to cram twice as many cores and threads with the same L3 cache onto a die that is only 10% larger than the Zen 4 CCD. The Zen 4C CCD, codenamed “Dinoysus,” has a -35.4% lower core area overall, and nearly every feature of the CCD has been decreased by -35% to -45%.

Also Read: