Intel offers a new Lunar Lake system-on-chip (SOC) with high efficiency and high performance after lifting the veil. This article takes a deep dive into various aspects of Lunar Lake: the P-Core and P-Core architecture, and more.

More About the Intel Lunar Lake CPU Architecture

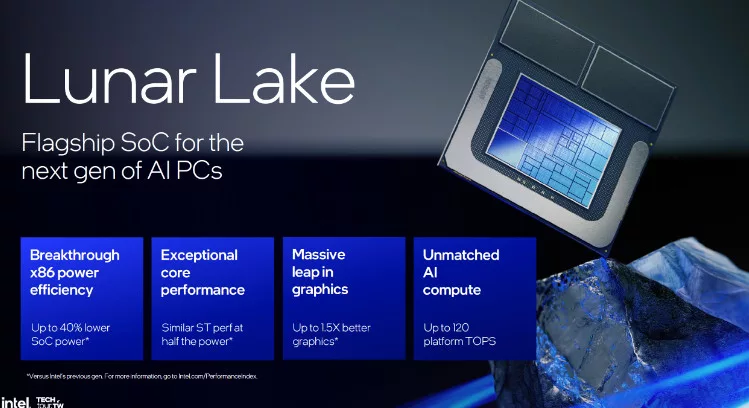

Lunar Lake has become a bit of an inside joke in the semiconductor world since it was first shown to the public, thanks to its claims of innovation bringing with it a paradigm shift in SOC technology. Intel is looking to provide an inside look at the workings of this brand-new chip with its official unveiling. Featuring Martian Exoplanet-compatible tech to power new AI PC platforms such as Microsoft Copilot+, Lunar Lake achieves:

- Breakthrough x86 power efficiency

- Exceptional core performance

- Massive leap in graphics capabilities

- Unmatched AI computing prowess

Prior to diving into the weeds, here is a high-level look at Intel’s Lunar Lake architecture. The construction starts with several packaging technologies packaging multiple different tiles.

The seven main components of Lunar Lake SOC begin with the interposer package containing memory, stiffener, and the Base Tile. Paired with the Platform Controller Tile, the compute tile forms the Base Tile using the Foveros interconnect. Lunar Lake’s tile count is significantly lower than that of the previous Meteor Lake design, which should boost efficiency and help prevent latency overhead. The compute tile is fabricated on TSMCs 3nm N3B process, with the Platform Controller die on TSMCs 6nm N6 process.

Lunar Lake: According to the leaks, this CPU will offer 16 and 32 GB LPDDR5X memory amounts and packs on-package memory. It will be able to reach up to 8533 MT/s per chip, using two 32 GB interconnected dies. This memory configuration offers significant power savings and area efficiency compared to traditional PCB-embedded designs.

Shifting to Lunar Lake it has an 8-core hybrid design but it’s using 4 of each type of core, so a 4+4P/E-Core configuration remains. Supporting these cores is a new Thread Director. P-Cores: PPA-optimized cores with improved single-threaded performance and large L2 and L3 cacheSizes In contrast E-Cores bring L2 Cache and Vector & AI throughput by x2.

The new Xe2 GPU will feature eight Xe cores, upgraded Ray Tracing Units, and XMX support. The SOC itself has a very high 120 Platform TOPs performance driven mainly by the NPU, GPU, and CPU.

Intel plans to launch Lunar Lake in Q3 with general availability coming in Q4 2024 with over 80 designs across 20 partners in tow. Additionally, Intel announced a new AI PC developer kit based on the Lunar Lake SOC, enabling developers to create and optimize AI PC experiences. This Dev Kit will also support future CPUs like Panther Lake. Moving on to architectural deep dives:

- Intel Lion Cove P-Core Architecture Deep Dive: Lion Cove – One Of Lunar Lake’s Key Architectures, And Improving Upon Everything This core naturally enhances single-threaded performance per watt/area efficiency by implementing new AI-based self-tuning controller and lower clock levels, without needing for 2x cores as outsourcing.

- Lunar Lake E-Core Architecture in Depth: Lunar Lake, like Skymont’s E-Core architecture, is focused on efficiency and scalability. Skymont delivers a larger IPC gain over Crestmont by making the Prediction blocks better, Widening the decode, and Performance of the vector is much improved.

Additionally, NPU 4 in Lunar Lake is twice as power efficient and 48 Peak TOPS more performant than its previous generation (NPU 3). This SOC also features updated connectivity, including Wi-Fi 7 and Thunderbolt 4 support, promising improved speeds and productivity.

Security remains a focal point for Lunar Lake SOCs, with built-in hardware security engines ensuring robust protection. While specific SKU details, performance metrics, and pricing are yet to be disclosed, Lunar Lake SOCs are expected to ship next quarter, heralding a new era of computing innovation.