AMD has announced the AMD Versal Premium VP1902 adaptive system-on-chip (SoC), which holds the distinction of being the world’s largest adaptive SoC. This chipset-based device is specifically designed to simplify the verification process for complex semiconductor designs. With twice the capacity of the previous generation, the VP1902 adaptive SoC empowers designers to confidently innovate and validate application-specific integrated circuits (ASICs) and SoC designs, accelerating the introduction of next-generation technologies to the market.

AMD unveils the world’s largest FPGA-based adaptive SoC for emulation and prototyping

The growing complexity of AI workloads necessitates advanced solutions in chip development to meet the demands of tomorrow. FPGA-based emulation and prototyping offer unparalleled performance, enabling faster silicon verification and allowing developers to shift their focus to software development well before silicon tape-out. Leveraging its acquisition of Xilinx, AMD brings over 17 years of leadership and six generations of high-capacity emulation devices to the table, with each generation nearly doubling in capacity.

Kirk Saban, Corporate Vice President of Product, Software, and Solutions Marketing, Adaptive and Embedded Computing Group at AMD, emphasized the company’s commitment to delivering foundational computing technology that enables its customers. In the realm of emulation and prototyping, this means providing the highest capacity and performance possible. With the VP1902 adaptive SoC, chip designers can confidently emulate and prototype next-generation products, accelerating advancements in AI, autonomous vehicles, Industry 5.0, and other emerging technologies.

Confident Emulation and Prototyping of Next-Generation Designs

As the complexity of ASIC and SoC designs continues to grow, particularly with the rapid progress of AI and ML-based chips, thorough verification of both silicon and software prior to tape-out is crucial. The VP1902 offers industry-leading capacity and connectivity, boasting 18.5 million logic cells, a 2×2 increase in programmable logic density, and a 2×4 increase in aggregate I/O bandwidth compared to the previous generation Virtex UltraScale+ VU19P FPGA.

Accelerated Design Iterations with Unmatched Debug Capabilities

Effective debugging is essential during pre-silicon verification and concurrent software development to ensure timely and cost-effective project execution. The VP1902 adaptive SoC leverages the Versal architecture, including the programmable network-on-chip, to deliver up to 8×5 faster debugging compared to the previous VU19P FPGA.

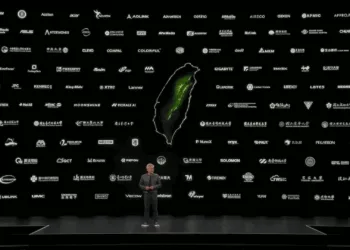

Development Tools and Ecosystem Collaborations

AMD’s Vivado ML design suite provides customers with a comprehensive development platform for rapid design, debugging, and validation of next-generation applications and technologies, reducing time to market. Enhanced features tailored for the VP1902 adaptive SoC include automated design closure assistance, interactive design tuning, remote multi-user real-time debugging, and improved back-end compilation, enabling end users to iterate IC designs more efficiently. AMD closely collaborates with leading EDA vendors such as Cadence, Siemens, and Synopsys to provide designers with a fully-featured and scalable ecosystem of solutions.

A sampling of the AMD Versal Premium VP1902 adaptive SoC is scheduled to begin in Q3 for early access customers, with production expected in the first half of 2024.