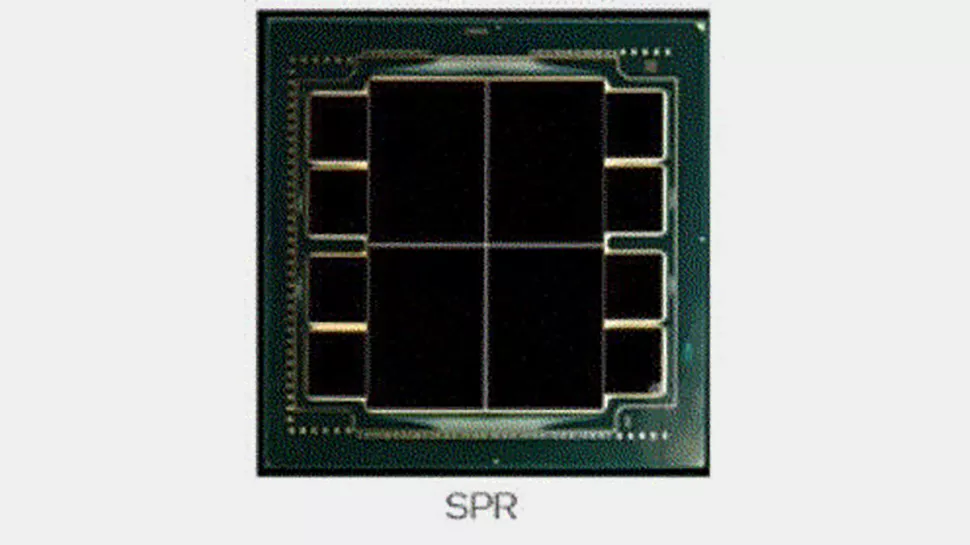

Intel has officially confirmed that its select models of the upcoming 4th Generation Xeon Scalable ‘Sapphire Rapids’ processors will feature on-package HBM memory. This news was confirmed by the chipmaker last year, however, the company is still to demonstrate an actual CPU equipped with HBM or revealed its DRAM configuration.

But, the International Symposium on Microelectronics hosted by IMAPS earlier this week, saw the first-ever showcasing of the processor with HBM and confirmed its multi-chipset design by intel. In the reveal, we found that each of the four Sapphire Rapids chiplets has two HBM memory stacks that use two 1024-bit interfaces.

If intel decided to go with KGSDs, then the HBM2E memory will provide Sapphire Rapids CPU with a whopping 3.68 TB/s of peak memory bandwidth but this will only be for 128GB of memory. HBM-equipped Sapphire Rapids comes in a large BGA form factor and will be soldered directly to the motherboard.

It’s also true that processors requiring a very high-performance memory subsystem like HBM always tend to feature loads of cores that work at high clocks as well as they feature a very high TDP.

Intel’s Sapphire Rapids processors will feature PCIe Gen 5 support with CXL 1.1 protocol for accelerators on top, a hybrid memory subsystem supporting DDR5 and HBM and they will come with the company’s Advanced Matrix Extensions (AMX) as well as AVX512_BF16 and AVX512_VP2INTERSECT instructions.

We also know from various leaks and rumours that Sapphire Rapids uses a multi-chip package with EMIB interconnects between the die. All the leaked features and details confirmed that the new and upcoming 4th Generation Xeon Scalable will be the first to use Intel’s latest packaging technologies and design paradigm.