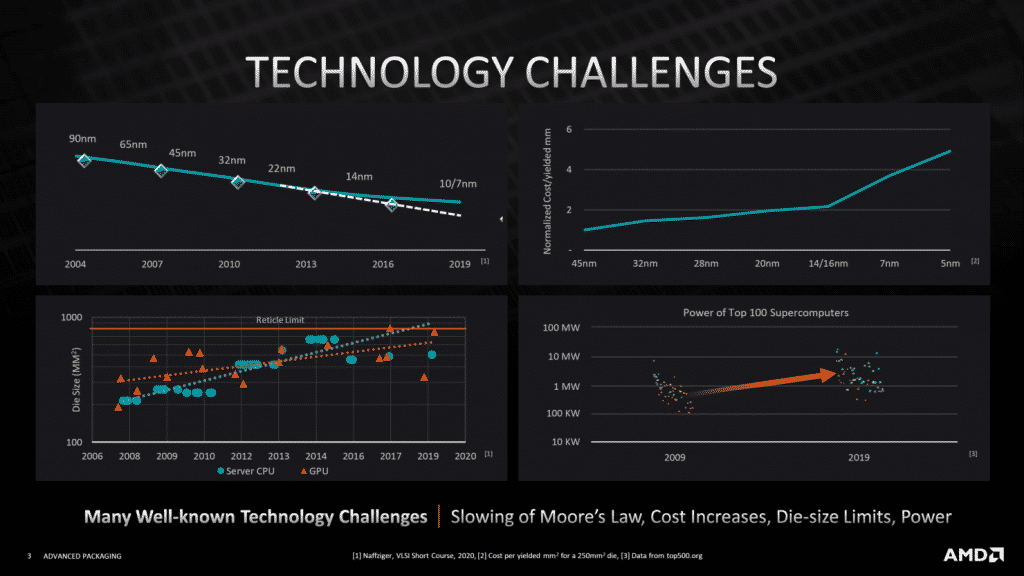

Obviously, Intel has made a huge announcement of its Alder Lake CPUs sporting up to 16 cores and 24 threads, which has again raised some enthusiasm among geeks and fans. So, AMD had to show what it has next, and it detailed its 3D V-Cache stacking technology, which they first unveiled at the Computex 2021.

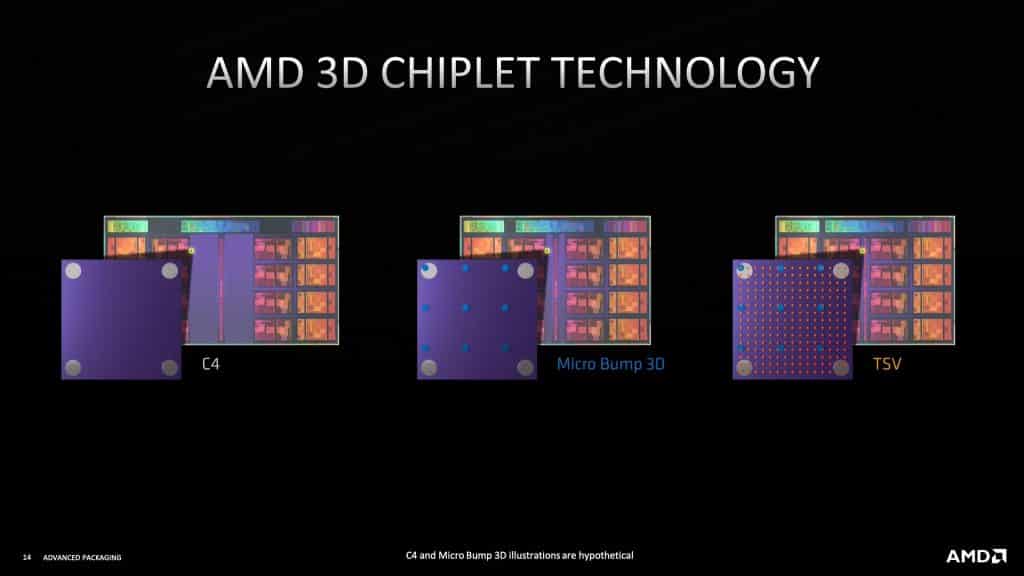

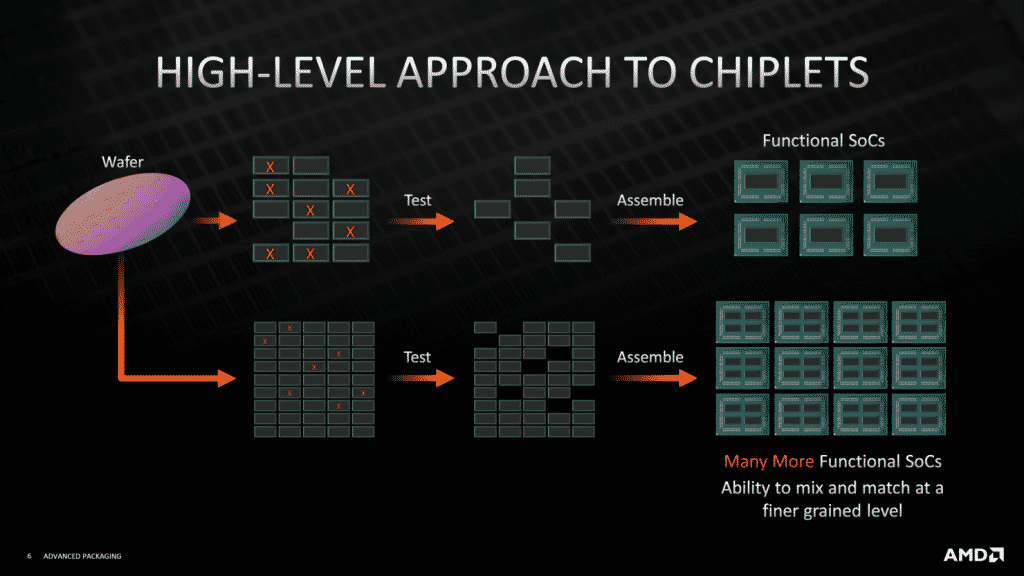

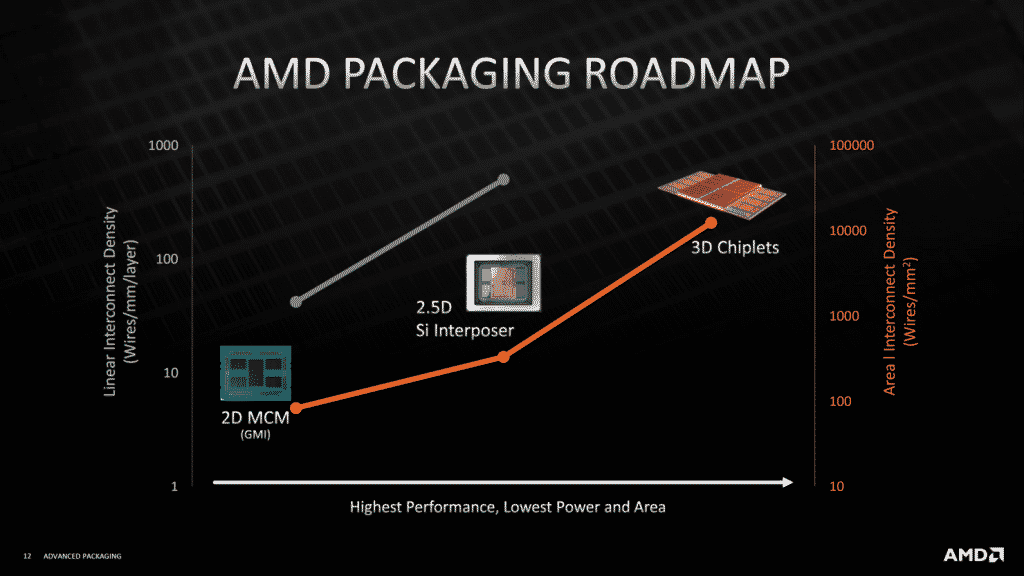

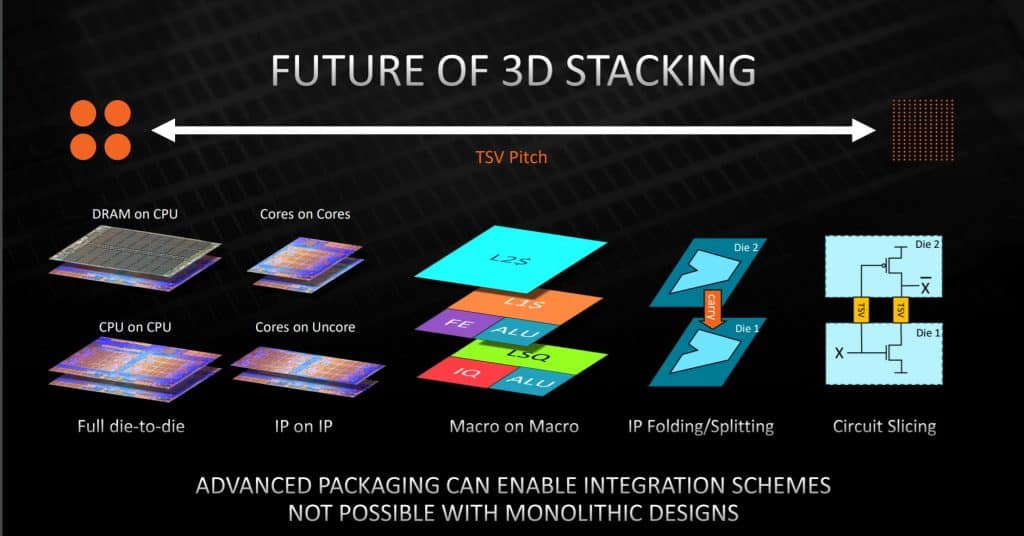

In Hot Chips 33 presentation, AMD also outlined the future of 3D stacking technology and shared the first details on its 3D V-Cache stacking. It demonstrated that the TSV (Through Silicon Via), a vertical inter-wafer or inter-die connection, sees an increase in bonds. The technology will be focusing on more complex 3D stacking designs.

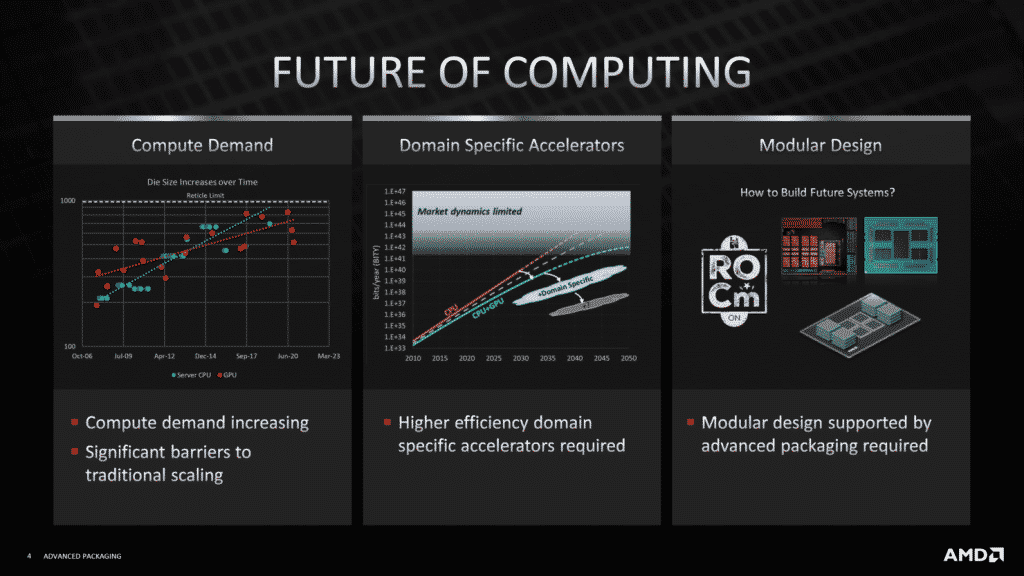

This will enable AMD to stack multiple dies on top of others like DRAM on CPUs or CPUs on CPUs or Cores on Cores and even IP on IP. So, the technology is progressing towards stacking separate modules on each other only to allow macroblocks to be stacked.

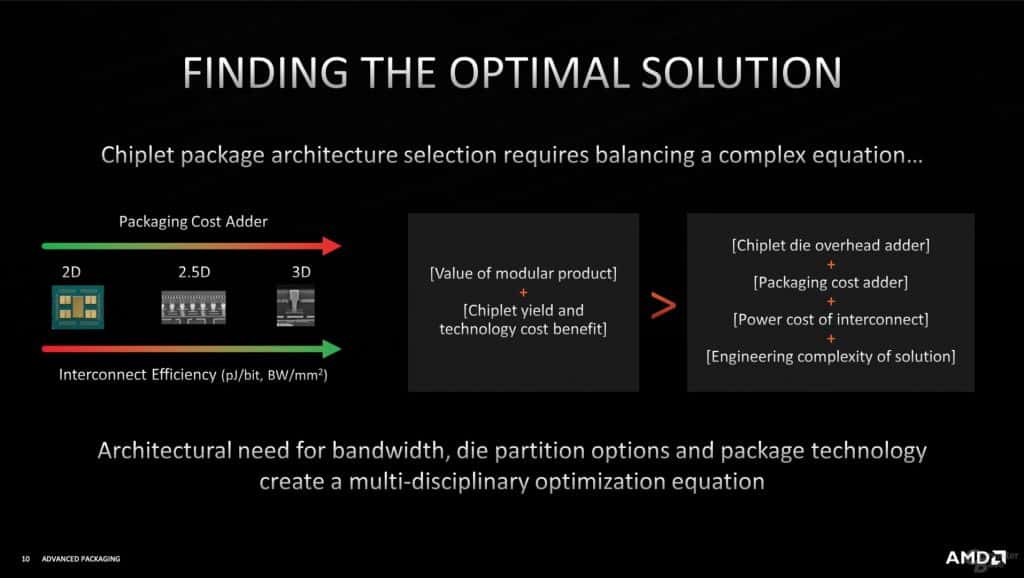

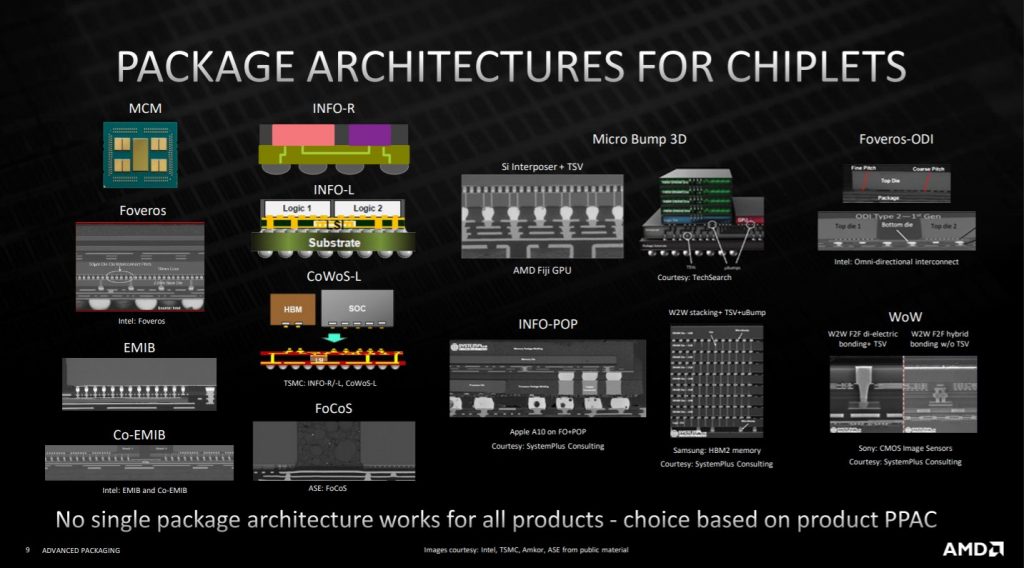

AMD even listed the possibilities of various package architectures as a substitute for 3D V-Cache stacking, including Intel’s Foveros technology. The TSV pitch will be so dense that module splitting or folding or even circuit splitting will be possible; this will completely change the landscape of future processors.

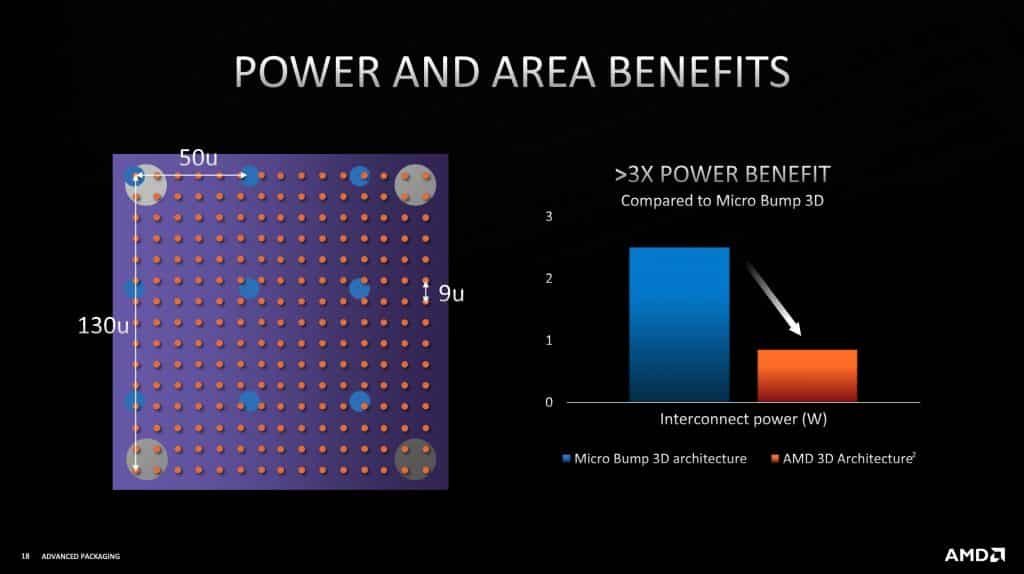

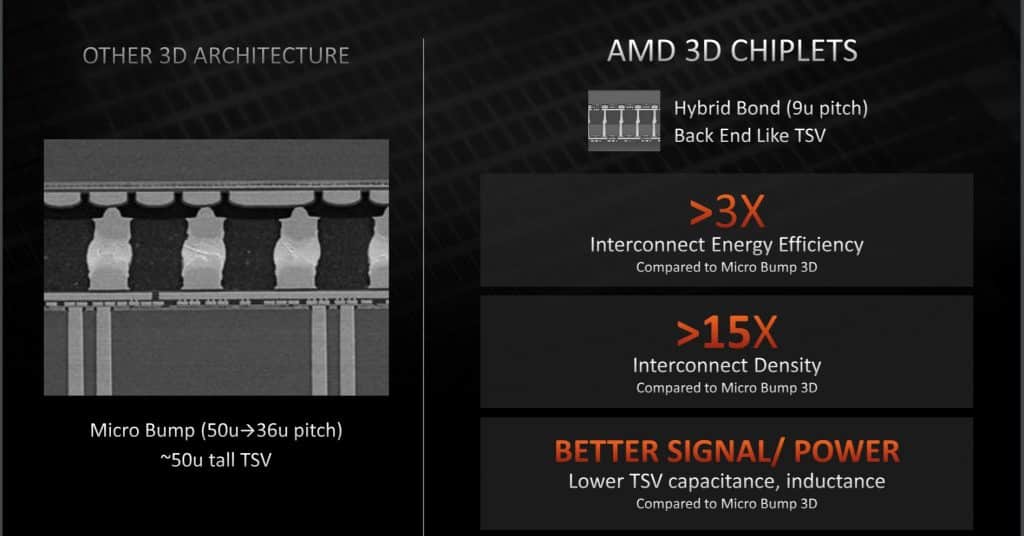

AMD has used a micro bump pitch of 9 microns that is even denser than future Intel Foveros Direct technology at 10 microns. Obviously, you will have efficiency benefits; the interconnect energy efficiency is rated at higher than 3 times compared to Micron Bump 3D.

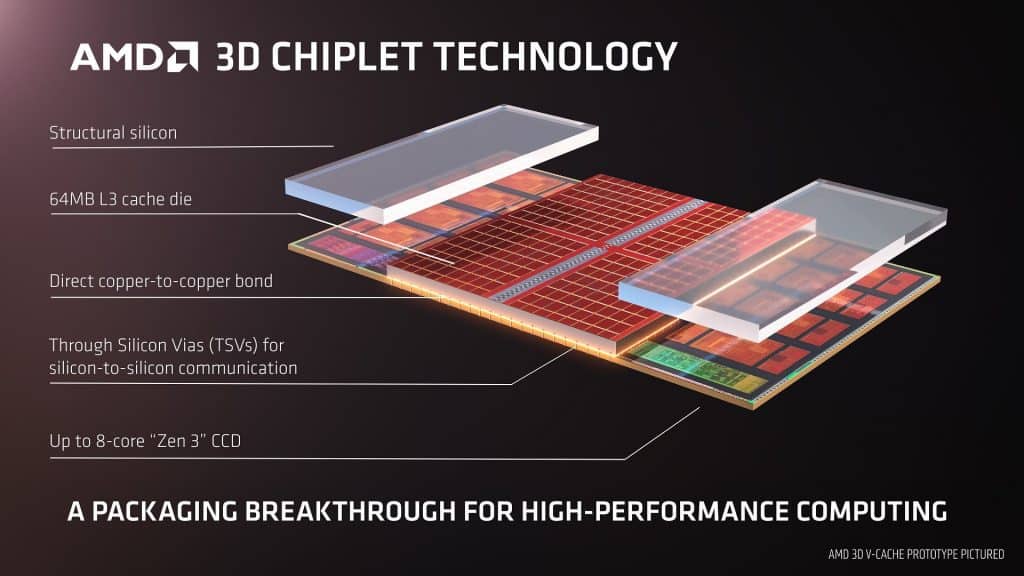

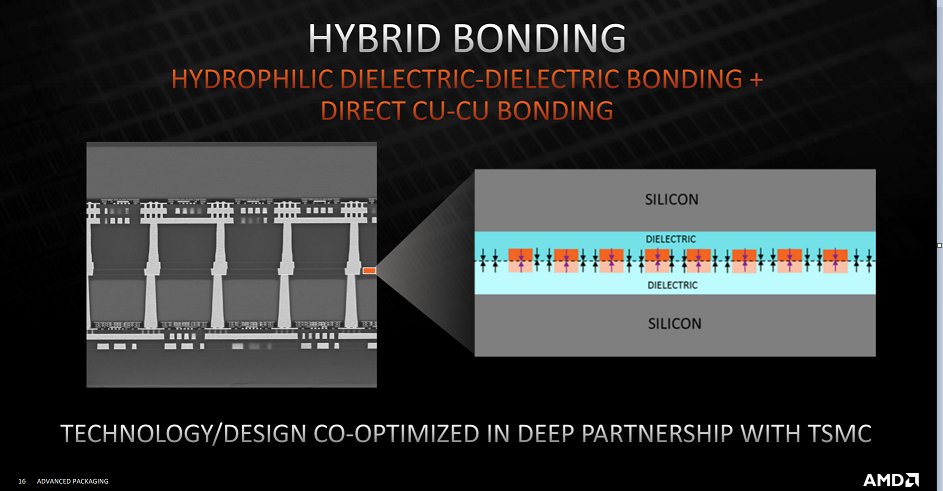

While the interconnect density is rated at more than 15 times higher than Micron Bump 3D, these 3D Chiplets also offer better signal/power thanks to lowering TSV capacitance and inductance. The technology wouldn’t have been possible without TSMC, as it uses a brand new hydrophilic Dielectric-Dielectric Bonding with Direct CU-CU bonding that was designed and co-optimized in deep partnership with TSMC.

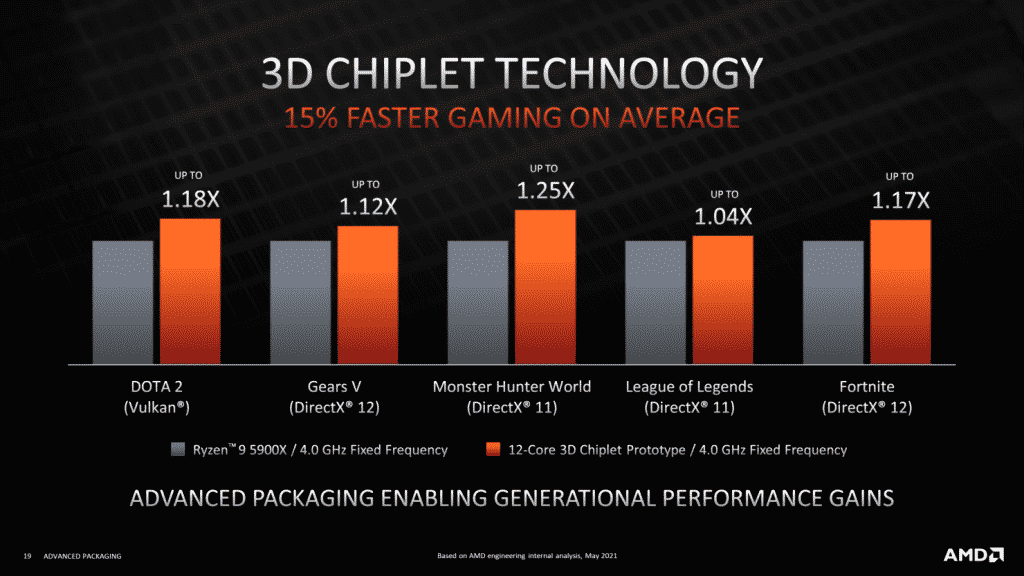

This means two individual silicons (chiplets) can now be bonded together using this technology. AMD also showed stacking 3D chipsets based on AMD’s Zen 3 CPU, featuring silicon to silicon TSV.

This automatically increases the Level 3 cache by 64MB, and as we remember, AMD showed 3D V-Cache technology in action on its best selling AMD Ryzen 9 5900X CPU with 32+64MB L3 cache. With the change in configuration and new packaging technique, you see an increase in the framerate by 15% on average, which is almost a generational uplift in performance.

So, indeed AMD, at Hot Chips 33 presentation, made it clear that if Intel will adopt Hybrid technology, it is also ready with its 3D V-Cache stacking technology and is in the high-performance computing race.

Back at Computex 2021, when the technology was unveiled, AMD also announced that Ryzen CPUs with 3D V-Cache would be mass-produced by the end of this year, so it will be interesting to see when AMD brings them to market to counter Intel.