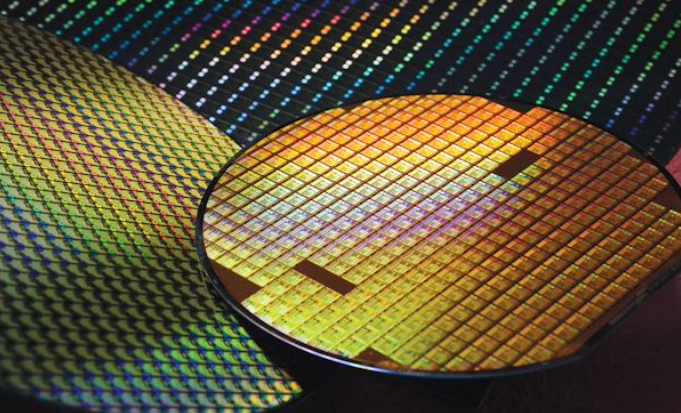

At the 2023 North America Technology Symposium, TSMC displayed its most recent technological advancements, including advancements in 2nm technology and new members of its 3nm technology family, which is the industry leader and offers a variety of processes tailored to satisfy various client demands.

There are three of these: N3P, an improved 3nm process for higher power, performance, and density; N3X, a process designed for high-performance computing (HPC) applications; and N3AE, which enables the earliest commencement of automotive applications on the most cutting-edge silicon technology.

Everything related to TSMC 3nm!

TSMC will be holding Technology Symposiums all over the world in the next months, with the first one happening in Santa Clara, California with over 1,600 customers and partners scheduled to attend. The Innovation Zone at the North American conference highlights the cutting-edge work of 18 new business start-ups.

Production of N3P is expected to begin in the second half of 2024, providing an additional speed boost of 5% at the same leakage, a reduction in power consumption of 5-10% at the same speed, and an increase in chip density of 1.04X compared to N3E.

With a focus on performance and the highest clock frequencies for HPC applications, N3X will reach volume production in 2025, offering 5% more speed than N3P at a drive voltage of 1.2V while maintaining the same increased chip density as N3P. Launching designs at the 3nm node for automotive applications is made possible by N3AE, or “Auto Early,” in 2023, which provides automotive process design kits (PDKs) based on N3E. This paves the way for the fully automotive-qualified N3A process, which will be released in 2025.

The development of TSMC’s 2nm technology, which uses nanosheet transistors, is proceeding steadily in terms of yield and device performance, and it is on schedule for production in 2025. There will be more than 1.15 times as many chips packed into the same area, with speeds up to 15% faster than N3E at the same power.

Using N4PRF to Break Through the Barriers of CMOS RF Technology For digital-intensive RF applications like WiFi 7 RF system-on-chip, TSMC is developing N4PRF, the industry’s most advanced CMOS radio frequency technology, in addition to the N6RF technology announced in 2021. When compared to N6RF, N4PRF will allow for 1.77 times the logic density while consuming 45% less logic power at the same speed.

Major new advances in TSMC’s 3DFabric system integration technologies, including Silicon Stacking and Advanced Packaging, include:

- Advanced Packaging – With up to 6 times the reticle-size (5,000mm2) RDL interposers and the ability to handle 12 stacks of HBM memory, TSMC is developing Chip on Wafer on Substrate (CoWoS) solutions to satisfy the demands of HPC applications.

- Design Support – To remove the barriers to 3D IC design, TSMC unveiled 3DbloxTM 1.5, the most recent version of its open standard design language. With the addition of automatic bump synthesis in 3DbloxTM 1.5, designers may more easily handle the complexity of huge dies with thousands of bumps, possibly cutting months off of design timeframes.

- 3D chip stacking – A useful method of 3D chip stacking was made possible by TSMC’s introduction of SoIC-P, micro bump variations of their System on Integrated Chips (SoIC) solutions. SoIC-P is an addition to TSMC’s already-available SoIC-X bumpless solutions for high-performance computing (HPC) applications.