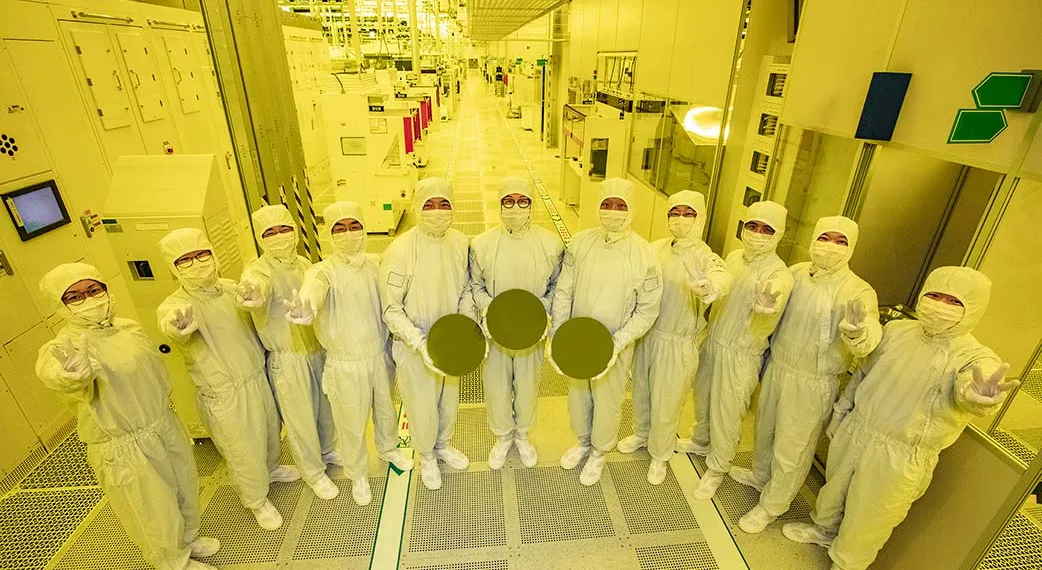

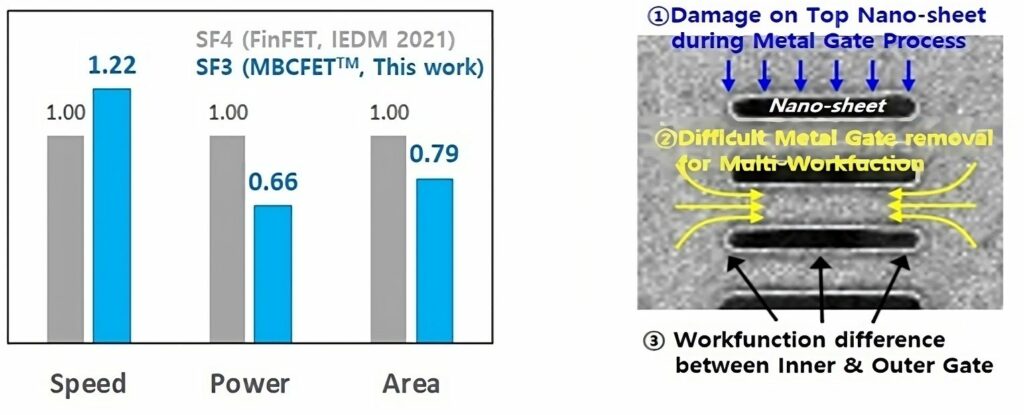

In order to compete with TSMC while simultaneously expanding its foundry business, Samsung plans to present its 3nm and 4nm technology at the VLSI Symposium 2023 in June. In terms of specifics, the Korean conglomerate will highlight the advantages of its SF3 and SF4X processes. The SF3 process will rely on GAA, or Gate All Around transistors, which the manufacturer refers to as MBCFETs, or Multi-Bridge-Channel Field-Effect Transistors, and will use Samsung’s 3nm GAP technology.

This strategy is believed to improve SF3, but strangely, Samsung has not directly compared this technology to its first-generation 3nm technology, implying that the difference may be minor.

SF4X is Samsung’s fourth-generation 4nm technology, offering a 10% performance gain and a 23% power-efficiency improvement over SF4, Samsung’s second-generation 4nm process.

TSMC’s N4P node, which is purportedly being used to mass produce the next Snapdragon 8 Gen 3 and Dimensity 9300, will compete with SF4X. Furthermore, this manufacturing method will involve the Taiwanese conglomerate’s N4X node, which is in its third 4nm generation.

The SF3 process is stated to be 22% faster than the SF4 process while operating at the same power limit and 34% more efficient when running at the same frequency and transistor count. There is also a 21% decrease in the logic area.

There are no details as to who will be the potential clients that have expressed interest in Samsung’s latest technologies, but previous rumours suggest that Qualcomm may be considering dual-sourcing for its Snapdragon chipsets.

Also Read: