New Granite Rapids Xeon CPUs from Intel with support for DDR5-6400 memory have been demonstrated. Intel will formally introduce their 4th Gen Sapphire Rapids Xeon range, which makes use of its 10nm ESF process node, on January 10, 2023. The HBM2e variations will also go on sale shortly after that, and the business subsequently intends to scale up production of its 5th Gen Emerald Rapids line.

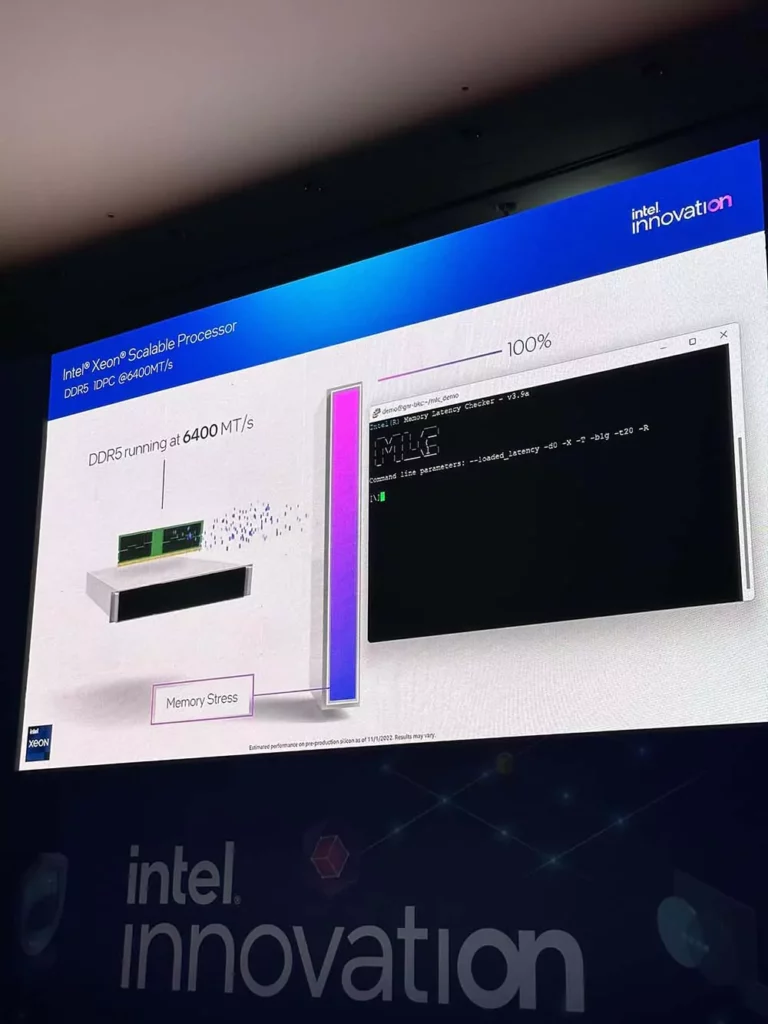

The blue team showcased its Sapphire Rapids platform running DDR5-5600 memory—an upgrade from DDR5-4800 and DDR5-5200—at its most recent Innovation 2022 event, which was held in Taipei, Taiwan. However, Intel also demonstrated a memory stress test of DDR5-6400 on its upcoming Xeon Scalable Processor during the demo run. The platform was running 1DPC (Single DIMM per Channel).

The ‘Intel 3’ process node will be the foundation for Intel’s Granite Rapids-SP Xeon CPUs, according to Intel (Formely 5nm EUV). The lineup is anticipated to debut between 2023 and 2024 because Emerald Rapids will just act as a bridge technology and not a true Xeon family replacement.

Although the precise number is not given, it is reported that Granite Rapids-SP Xeon chips will make use of the Redwood Cove core design and have enhanced core counts. During its ‘Accelerated’ speech, Intel did tease a high-level overview of its Granite Rapids-SP CPU, which appeared to have several dies bundled in a single SOC using EMIB. Along with high-bandwidth Rambo Cache packages, HBM packages are visible. The Compute tile appears to include 60 cores on each die, for a total of 120 cores, but we should anticipate that some of those cores will be disabled to improve yields on the new Intel 3 manufacturing node.

Despite Intel doubling its core count, they might not be able to match AMD’s disruptive multi-threaded and multi-core advantage because AMD will be boosting the core counts of its own Zen 4C EPYC portfolio with Bergamo, pushing out up to 128 cores and 256 threads. However, this is where Intel might start to catch up to AMD’s Zen architecture and reenter the server market in terms of IPC. The current information indicates that the chips would support 8-channel DDR5, PCIe 5.0, CXL 2.0, and PFR 4.0 and come in HBM variants. Earlier speculations had mentioned 12-channel DDR5 and PCIe 6.0 capability.

Also Read: