Imec, the world’s leading semiconductor research organisation, recently revealed its sub-1nm silicon and transistor roadmap at its ITF World event in Antwerp, Belgium. The roadmap provides a timeframe for the next major process nodes and transistor designs that the business will research and develop in its labs in collaboration with industry titans such as TSMC, Intel, Nvidia, AMD, Samsung, and ASML, among many others, through 2036.

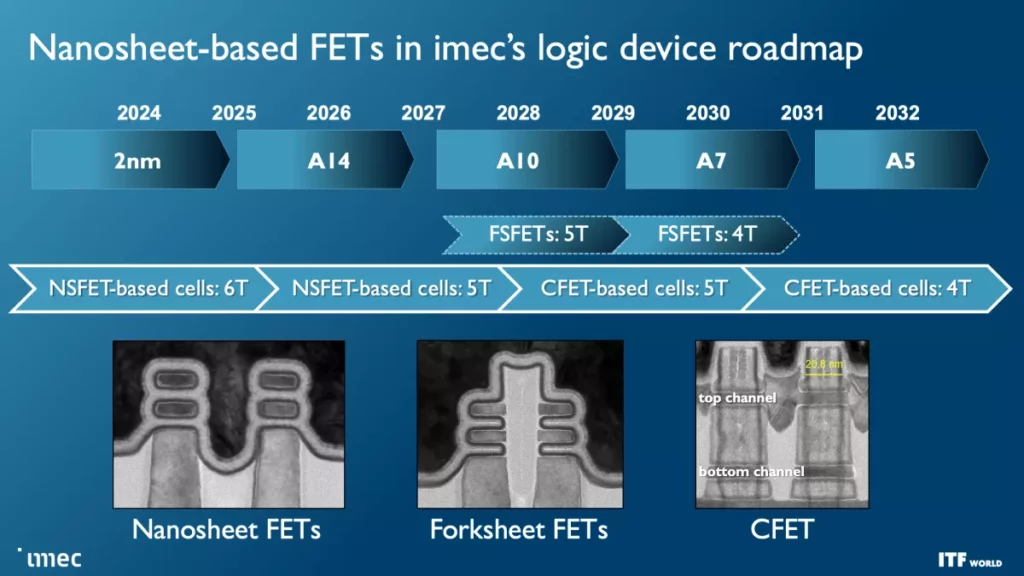

Imec’s plan includes sub-‘1nm’ process nodes as well as the transition from ordinary FinFET transistors to the revolutionary Gate All Around (GAA) nanosheet designs, which will start high-volume production in 2024. Imec’s roadmap includes forksheet designs at 2nm and A7 (0.7nm), followed by breakthrough designs like CFETs and atomic channels at A5 and A2.

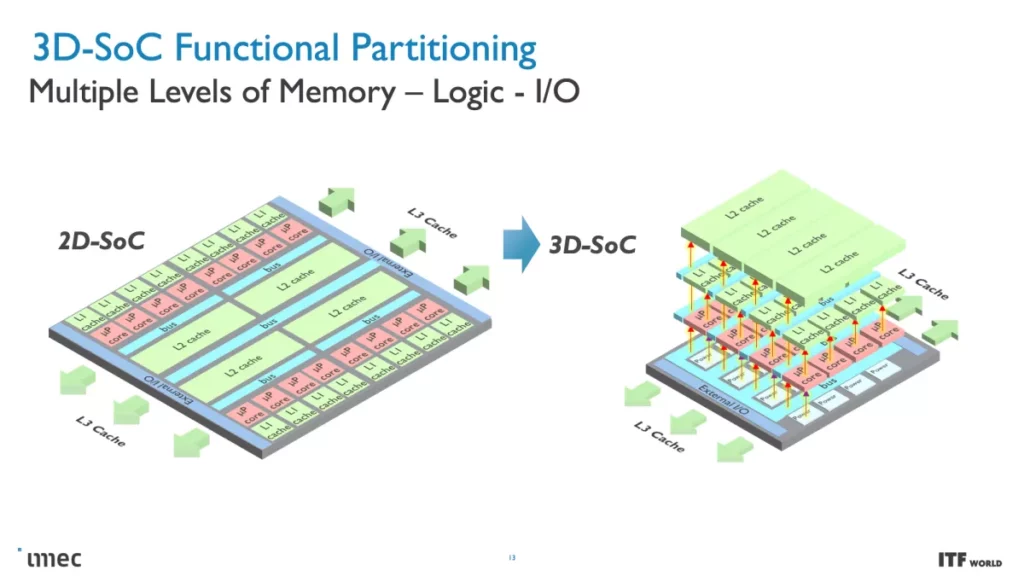

Imec’s concept of the CMOS 2.0 paradigm includes splitting the chips down even further, with caches and memory divided into their own units with distinct transistors and layered in a 3D layout above the other chip functions. This methodology will also primarily rely on backside power delivery networks (BPDN), which transport all power through the transistor’s backside.

The first goal of Ime will be faster and denser transistors, with the Gate All Around (GAA)/Nanosheet devices debuting in 2024 with the 2nm node, replacing the triple-gate FinFETs that power today’s cutting-edge gadgets.

GAA transistors provide increased transistor density and performance, such as faster transistor switching while using the same drive current as many fins. Because the channels are completely encircled by a gate, leakage is considerably reduced, and altering the channel width can optimise for either power consumption or performance.

Complementary FET (CFET) transistors will further reduce the footprint when they debut with the 1nm node (A10) in 2028, enabling for more densely packed standard cell libraries. Eventually, we’ll see CFETs with atomic channels, which will improve performance and scalability even further.

CFET transistors, about which you may learn more here, stack N- and PMOS devices on top of each other to achieve increased density. CFETs should signal the end of scaling for nanosheet devices and the visible roadmap.

Imec’s vision for future chip designs has culminated in CMOS 2.0, which includes completely 3D chip designs. Each level of cache would be built with the transistors best suited for the task, implying older nodes for SRAM, which is becoming increasingly relevant as SRAM scaling has slowed dramatically.

Because of SRAM’s restricted scaling, caches now use a larger percentage of the die, increasing cost-per-MB and discouraging chipmakers from employing larger caches. These CMOS 2.0 techniques will use 3D stacking technologies, such as wafer-to-wafer hybrid bonding, to construct a direct die-to-die 3D interconnect, as described here.

Also Read: