AMD will launch its upcoming Zen 4 architecture next year both for its mainstream Ryzen CPUs and its server EPYC processors. According to ComputerBase, these details have given a better overview of the AMD SP5 socket for the next-generation EPYC 7004 “Genoa” server CPU series.

All thanks to the GIGABYTE hack that has revealed sensitive info for both AMD and Intel processors, new details about AMD SP5 and AM5 platforms have been leaked simultaneously. Read here about AM5: The latest leak reveals the TDP requirements of AMD’s AM5 LGA 1718 socket’s for next-gen Ryzen CPU’s

These screenshots from AMD documents have been posted by @KittyYYuko, which could soon disappear if AMD strikes a DMCA claim.

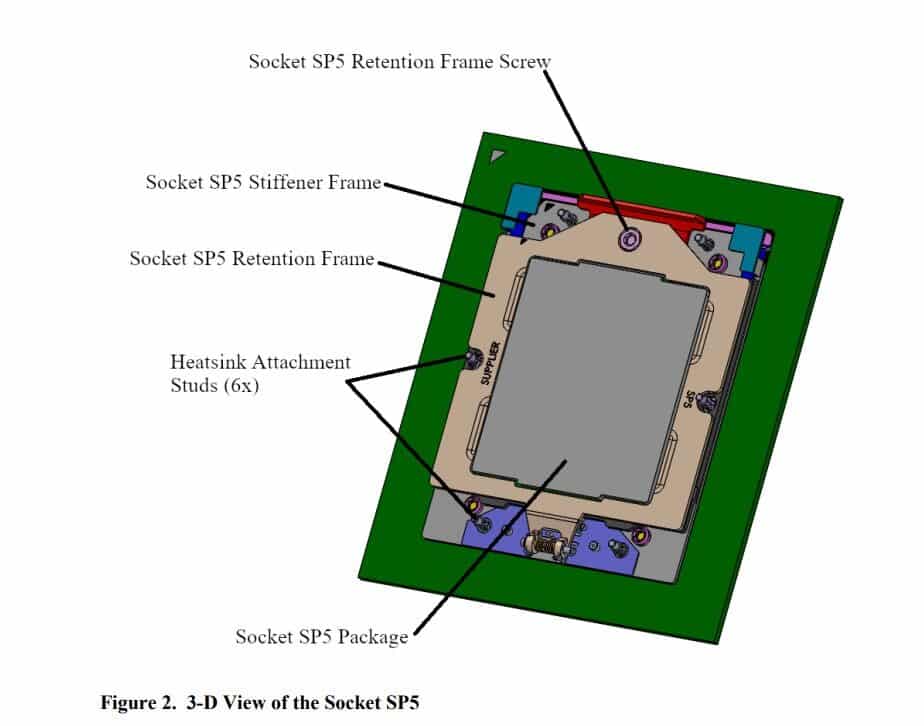

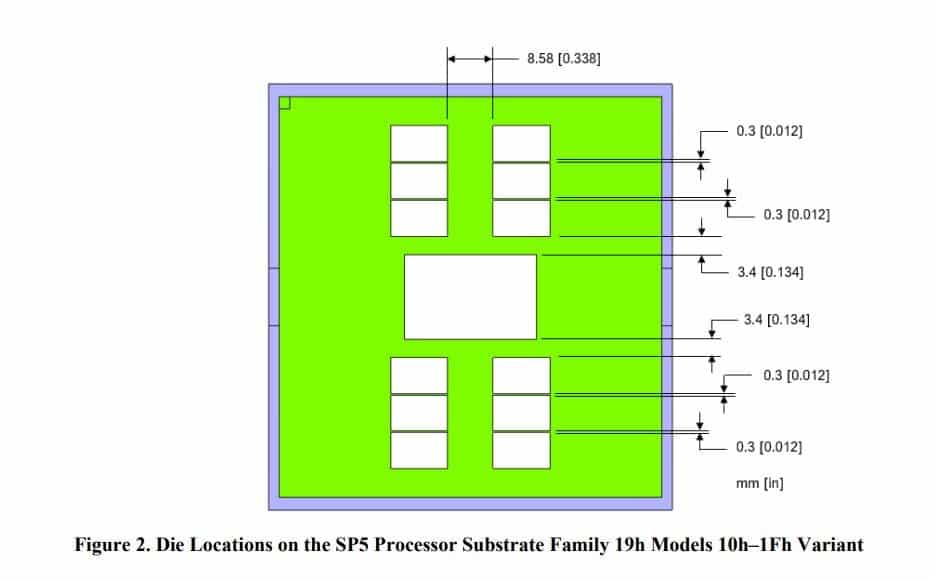

The images detail the SP5 socket totally, showing the actual product overview and the socket design, it even goes on to demonstrate the die locations on the SP5 processor, with the silicon positioning and spacing along with the number of cores & threads on it.

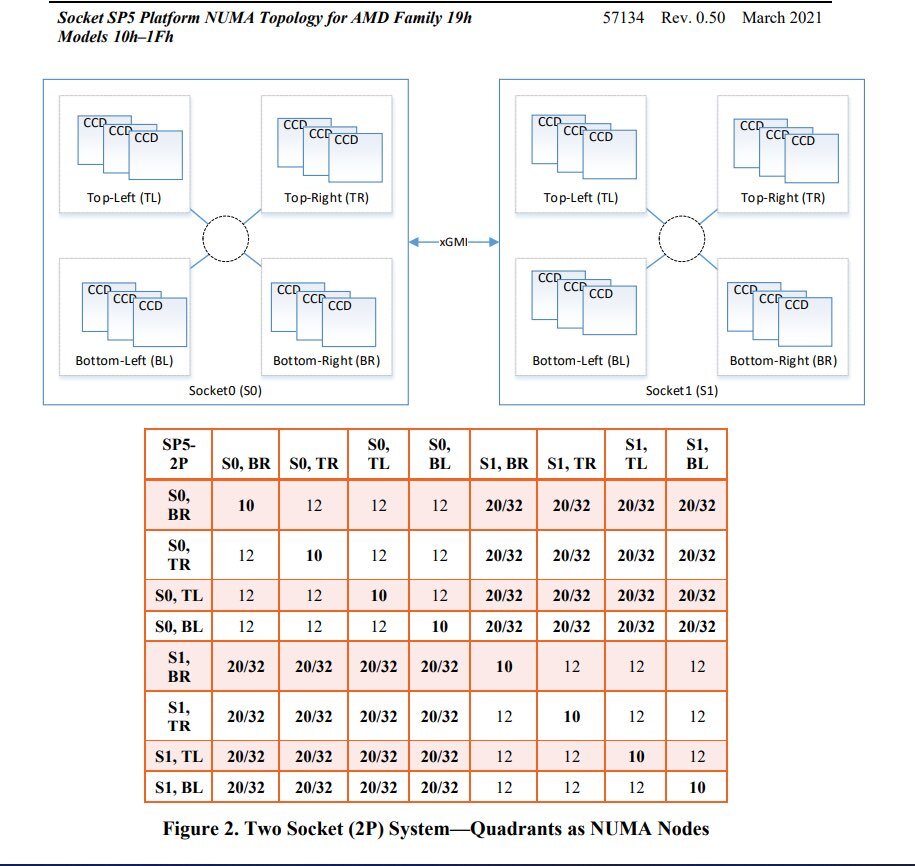

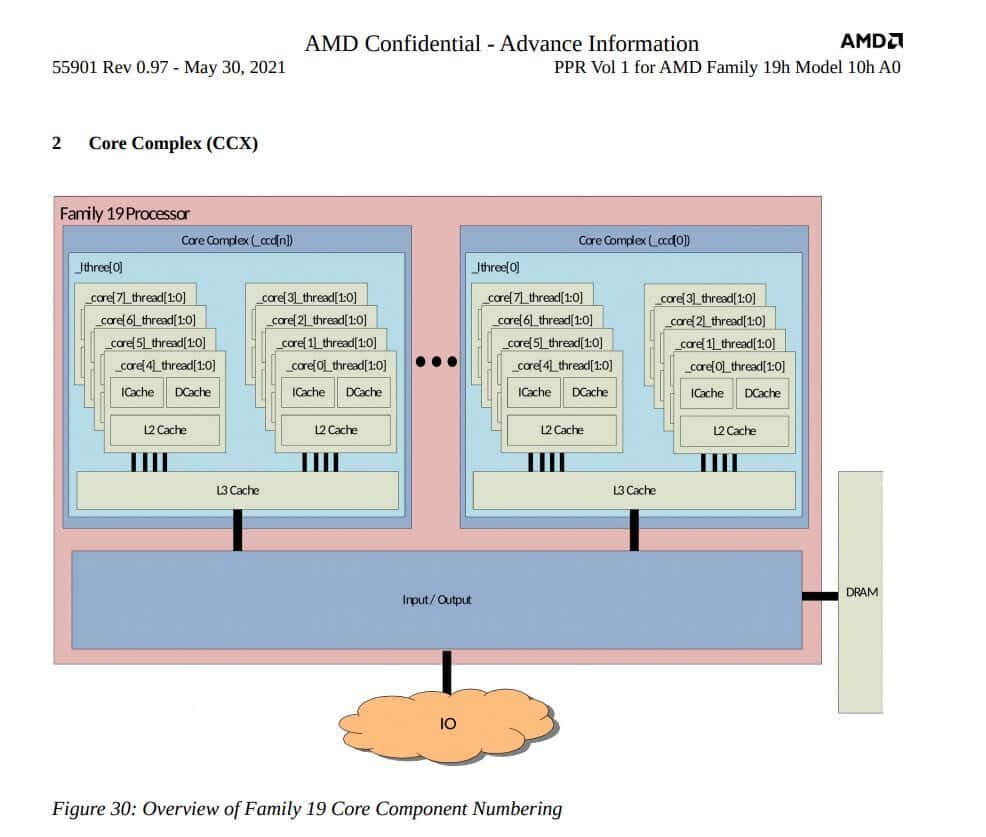

So, you see there are 12 CCDs on the chip, 3 on the top left, 3 on top right while there are 3 at the bottom left and 3 at the bottom right. All these CCDs will be connected with an I/O die, much like last gen, but each CCD that supports up to 8 cores will have their own L3 cache.

Much like previous rumours, with these diagrams and confidential info it can be confirmed that the EPYC 7004 series will feature up to 12 CCDs and each of them will have 8 cores, which means you will have up to 96 cores and 192 threads.

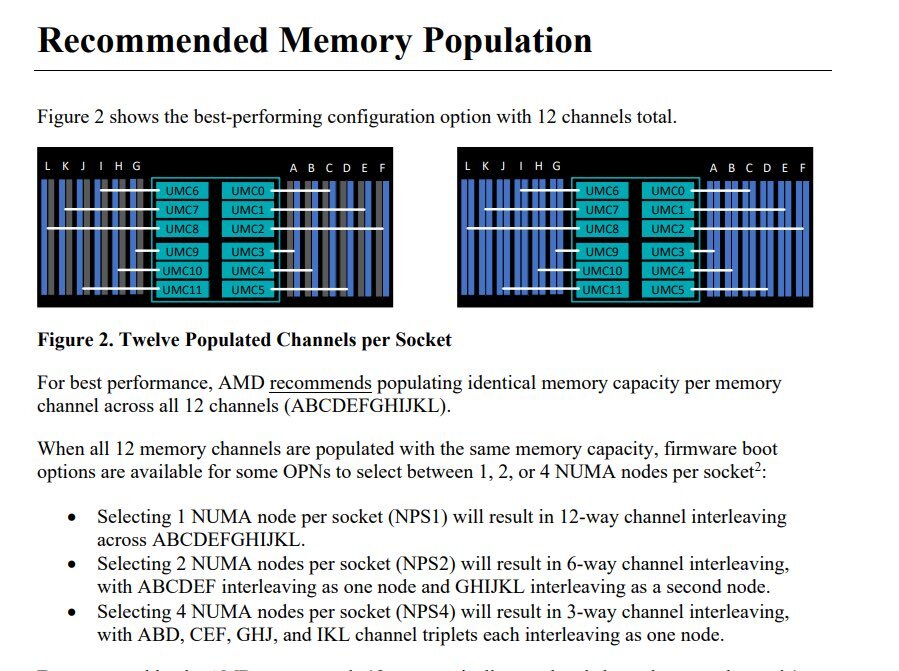

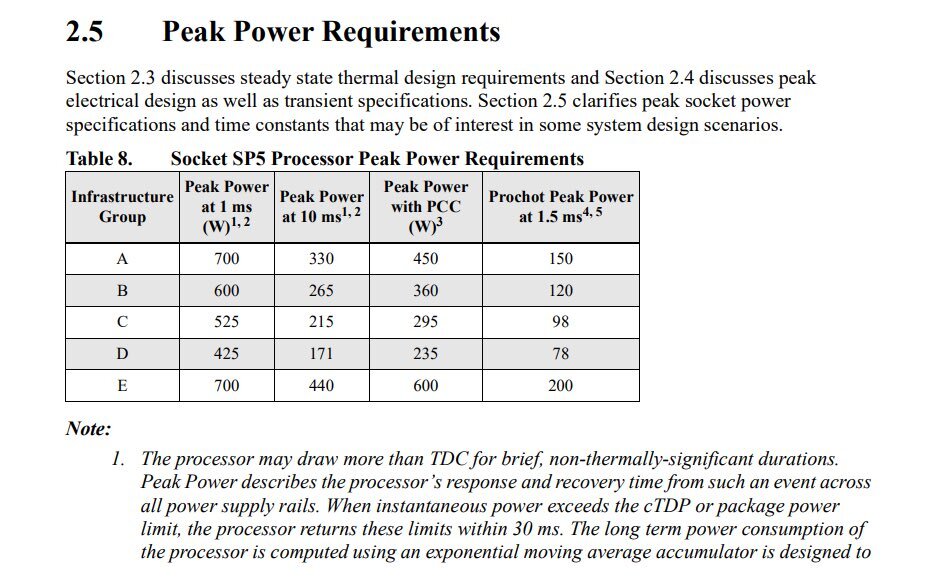

Not only this, upcoming Zen 4 based EPYC Genoa CPUs will support 12-channel DDR5 memory and the top-of-the-line SKU will have a default 320W TDP and a maximum of 400W. These AMD chips are scheduled to launch next year and until CES 2021, we do not have any exact launch dates.

via Videocardz