AMD Zen 6 Venice CPUs surface in Linux kernel patch with new CPU IDs, revealing EPYC Venice specifications and Weisshorn codename details.

The tech world is buzzing with excitement as AMD’s next-generation Zen 6 architecture has been spotted in Linux kernel patches, providing our first concrete glimpse into the company’s revolutionary EPYC Venice processors. This discovery marks a significant milestone in AMD’s roadmap toward dominating the server and workstation markets with unprecedented performance capabilities.

Table of Contents

AMD Zen 6 Venice CPUs Surface in Linux Development

Linux kernel developers have uncovered compelling evidence of AMD’s Zen 6 Venice processors through newly released CPU identification patches. The discovery, first reported by prominent hardware leaker InstLatX64, reveals specific CPU IDs that correspond to the mysterious “Weisshorn” codename—AMD’s internal designation for Venice workstation processors.

This early Linux enablement work demonstrates AMD’s commitment to supporting open-source platforms, a strategy that has consistently given the company a competitive edge over Intel in enterprise markets. The patches indicate that AMD is prioritizing professional-grade processors for initial Zen 6 deployment.

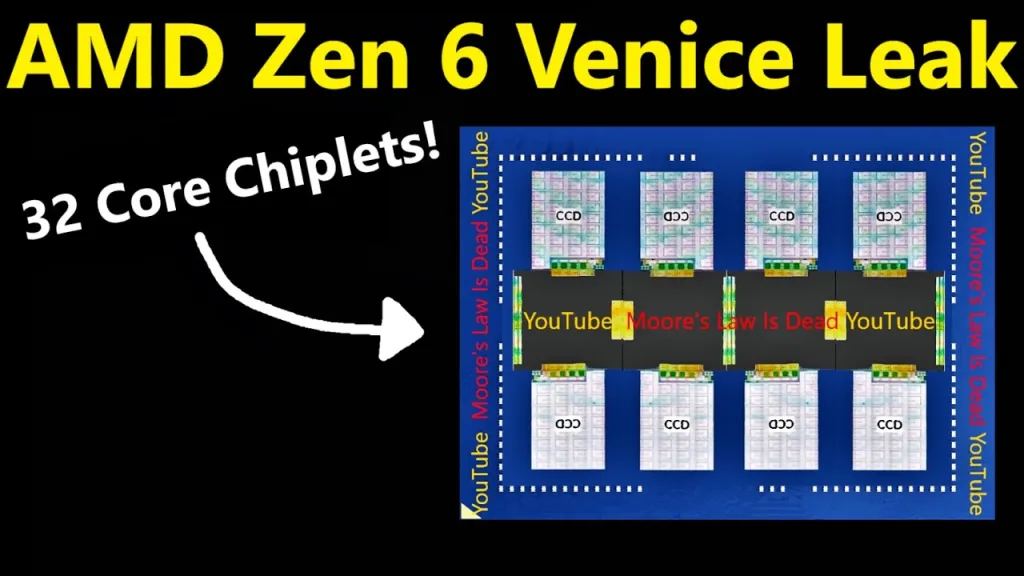

Decoding the Venice CPU Architecture

The leaked Linux patches reveal fascinating details about AMD’s Zen 6 Venice architecture that will reshape the computing landscape:

| Specification | EPYC Venice Details |

|---|---|

| Manufacturing Process | TSMC N2 (2nm) |

| Maximum Cores | 256 cores |

| Maximum Threads | 512 threads |

| CCD Configuration | Up to 8 CCDs |

| Architecture Mix | Zen 6 + Zen 6C cores |

| Target Market | Data centers, HPC, AI workloads |

CPU ID Breakdown and Codename Analysis

The Linux kernel patches reveal multiple CPU IDs under the Zen 6 feature flag:

- B50F00 (Weisshorn): Primary EPYC Venice processors

- B90F00: Likely Venice-Dense variant

- BA0F00: Potential AI accelerator integration

- BC0F00: Undisclosed Venice variant

The “Weisshorn” codename follows AMD’s tradition of using Alpine peak names for processor families, suggesting this represents the flagship Venice workstation lineup. This naming convention aligns with previous “Breithorn” codenames used for earlier EPYC generations.

Professional Focus Over Consumer Markets

AMD’s current Zen 6 development appears heavily focused on enterprise and AI markets, with consumer variants taking a backseat. The Linux patches specifically target AMD’s professional portfolio, including data center solutions and Instinct AI accelerators.

This strategic approach reflects market realities where AI workloads and cloud computing drive the highest profit margins. By prioritizing these segments, AMD can maximize revenue while establishing dominance in rapidly growing markets.

Venice vs. Medusa Ridge: Professional vs. Consumer

While Venice targets professional markets, AMD’s consumer Zen 6 offerings will arrive under the “Medusa Ridge” codename. These desktop processors will feature more modest specifications tailored for gaming and content creation:

- 12-core configurations: Mainstream gaming performance

- 24-core variants: Content creation powerhouses

- 32-core models: Enthusiast-grade processing

- Up to 128MB L3 cache: Enhanced gaming and productivity performance

Revolutionary 2nm Technology Impact

TSMC’s N2 process node represents a quantum leap in semiconductor manufacturing, enabling AMD to pack unprecedented transistor density into Venice processors. This 2nm technology delivers:

- 50% power efficiency improvements over current generation

- Massive core count scaling up to 256 cores per socket

- Enhanced AI acceleration capabilities for machine learning workloads

- Superior thermal characteristics for dense server environments

Market Implications and Competition

AMD’s early Linux enablement for Zen 6 Venice signals aggressive market positioning against Intel’s upcoming processors. By establishing software compatibility months before hardware availability, AMD ensures seamless enterprise adoption and maintains its server market momentum.

The 256-core capability positions Venice as a direct challenger to specialized AI processors, potentially capturing market share from NVIDIA and Intel in the lucrative AI inference market.

Frequently Asked Questions:

Q: When will AMD Zen 6 Venice processors be available?

A: While no official date exists, Linux kernel patches suggest a 2026 launch timeframe for EPYC Venice processors.

Q: What makes Zen 6 Venice different from current EPYC processors?

A: Venice features 2nm manufacturing, up to 256 cores, and hybrid Zen 6 + Zen 6C architecture for unprecedented performance density.

Q: Will Zen 6 Venice support consumer applications?

A: Venice targets enterprise markets. Consumer Zen 6 processors will use the “Medusa Ridge” architecture with 12-32 core configurations.

Q: What is the Weisshorn codename?

A: Weisshorn represents AMD’s internal designation for Venice workstation processors, following their Alpine peak naming convention.

Q: How does 2nm technology benefit Venice processors?

A: TSMC’s N2 process enables massive core scaling, improved power efficiency, and enhanced AI acceleration capabilities.

Q: Will Venice compete with Intel’s server processors?

A: Yes, Venice’s 256-core capability and 2nm technology position it as a direct competitor to Intel’s next-generation Xeon processors.

Conclusion

AMD’s Zen 6 Venice processors represent a paradigm shift in server computing, combining cutting-edge 2nm technology with unprecedented core counts. The Linux kernel discoveries provide exciting insights into AMD’s ambitious roadmap, suggesting a future where 256-core processors become the new standard for enterprise computing.

As development accelerates, Venice promises to cement AMD’s leadership in server markets while establishing new performance benchmarks that will influence computing for years to come.