According to rumours, the AMD Zen 5 core architecture will have a completely revised cache design, which will help boost IPC for next-generation CPUs. AdoredTV, which recently shared the most recent details about AMD’s upcoming Zen 5 architecture, is the source of the rumour. AMD’s Zen 4 architecture isn’t quite finished, but the company has the first Zen 5 samples in early prototype form in its labs.

Work has been underway on the AMD Zen 5 core architecture, also known as “Nirvana,” since 2020 or 2021. According to recent reports, the first Zen 5 products are scheduled to launch in 2024 and will be constructed entirely from scratch.

The internal CPU architecture will undoubtedly undergo significant changes because it is a completely new design. AdoredTV, a tech publication, has detailed some potential changes.

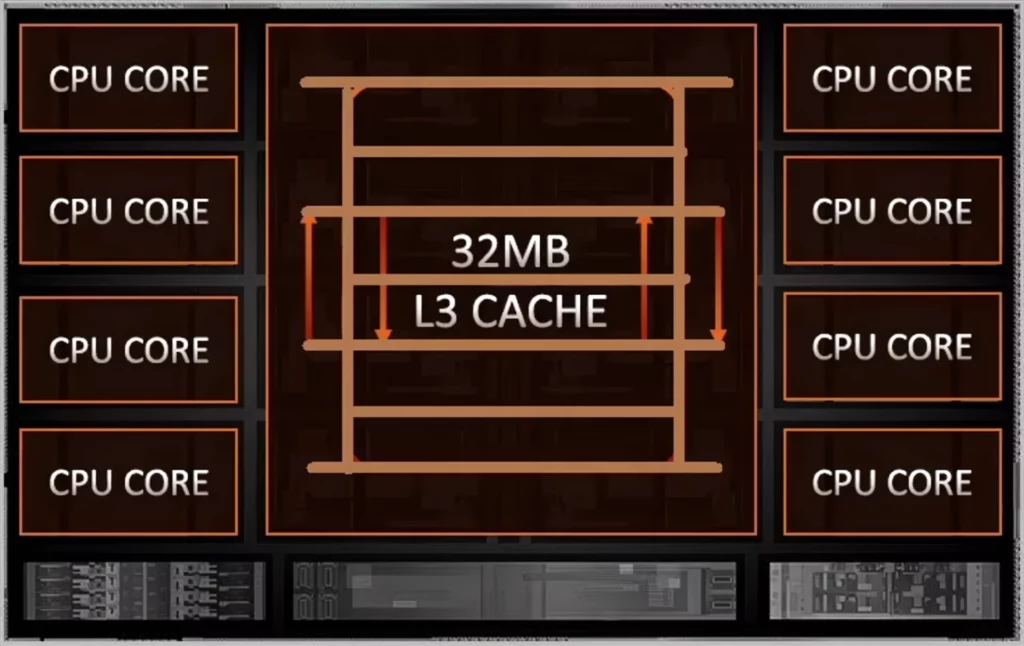

The use of a new “Ladder” shared cache is the first significant change rumoured for AMD’s Zen 5 CPU core architecture. The L3 cache in the earlier Zen architectures was divided into two 16 MB blocks that were shared by the two CCXs in each CCD. Only 16 MB of L3 cache pools could be accessed by a single CCX.

With Zen 3, AMD made a change and eliminated the dual CCX in favour of a single CCX with a shared 32 MB L3 cache pool connected to all 8 cores on the die in a ring configuration. With Zen 5, AMD is rumoured to change the design once more to a new 32 MB L3 “Ladder” cache.

Comparing this structure to the ring interconnect design, it is claimed to significantly reduce inter-core latency and communication bottlenecks. The figure presented here is only intended to give a general idea of how the new L3 cache structure would operate; we are unable to predict with certainty whether the L3 cache will remain at 32 MB or increase in size.

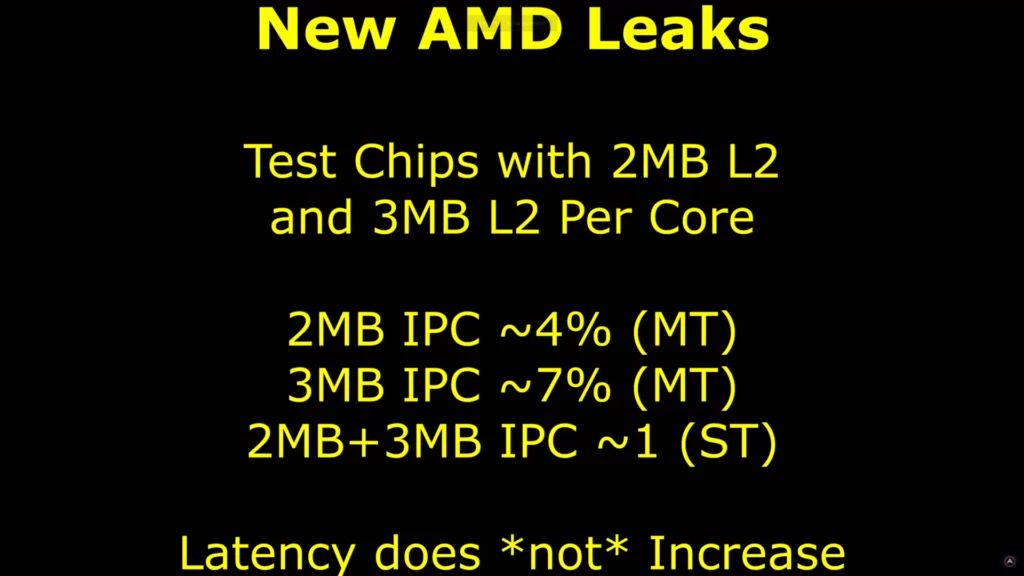

In AMD Zen 5, the L2 cache is said to receive a boost.

According to AdoredTV, each AMD Zen 5 CPU core’s L2 cache will increase. According to them, AMD has both 2 MB and 3 MB L2 cache per core chips in its testing facilities, though they might or might not be Zen 5 components. If they are Zen 5 chips, this will be a 2x and 3x improvement over the existing Zen 4 cores’ 1 MB cache per core, respectively.

The IPC can also directly benefit from the increased cache on the AMD Zen 5 CPU cores, with a 2 MB L2 cache per core providing gains of up to 4% and a 3 MB L2 cache per core providing gains of 7%.

In multi-threaded workloads, the gains are assessed, and in single-threaded workloads, the IPC benefits may be as low as 1%. Although all of this needs to be tested and confirmed when the chips launch, which is still a year away, latency won’t be affected by the addition of more cache per core as mentioned.

Also Read: