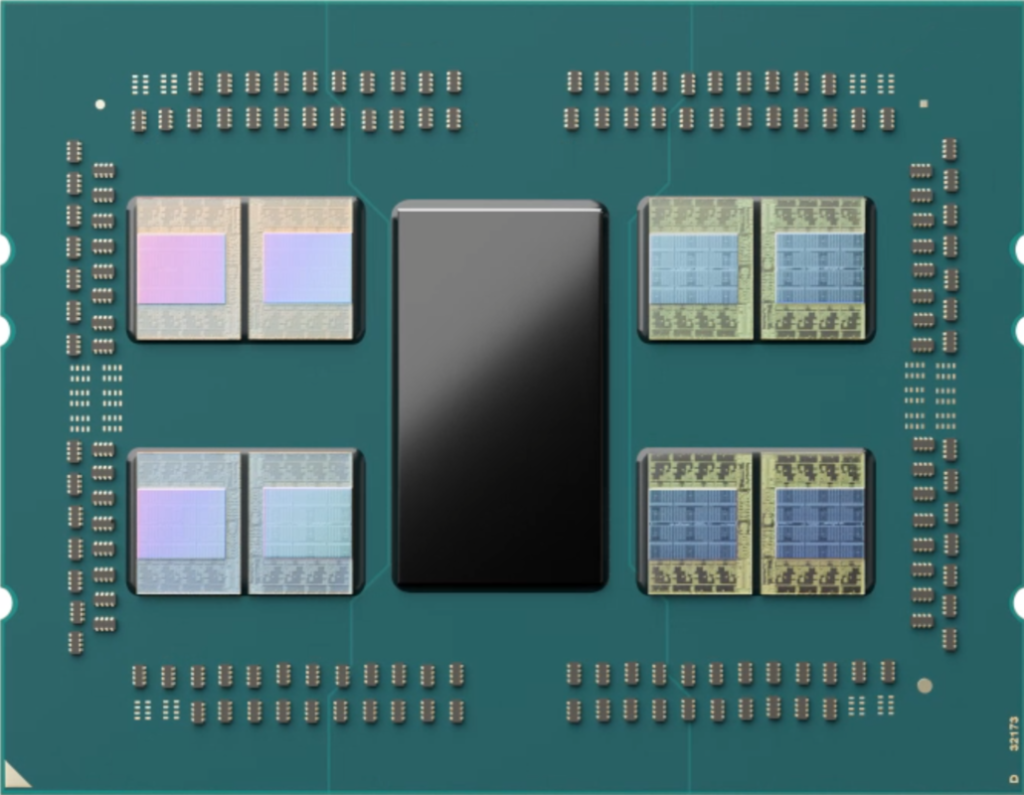

According to Moore’s Law is Dead, the successor to AMD’s EPYC Turin CPUs, which will contain Zen 5 cores, will be dubbed EPYC Venice and will use Zen 6 architecture. While the facts are scarce at the moment, given that this product isn’t slated to ship until 2025 or later, it appears that MLID obtained very early information about the codename, and AMD’s marketing has coined the term ‘Venice’ for its next-generation EPYC family. The EPYC Venice lineup, named after the capital of the Veneto area in northeastern Italy, is likely to be a massive improvement for servers.

The AMD Zen 6 cores are mentioned in some of the specifics, although it is unclear whether the red team will stick with the Zen naming scheme beyond 2025 or switch to something else. The EPYC name convention will be followed in the server portion.

According to reports, Zen 6, or the x86 architecture following Zen 5, will adopt a very hybrid core design method and will have over 200 cores, with up to 384 cores per socket. There’s no word on whether the CPU will work with the SP5 platform, although Turin and its Zen 5C follow-up appear to be the last EPYC chips for the forthcoming platform.

Here’s the video of the EPYC Venice leak

In terms of architecture improvements, the leaker also revealed that AMD plans to entirely rebuild the L2 and L3 cache systems. The design of the Infinity Cache will also undergo significant changes. HBM will also become the standard throughout the majority of the lineup, and the memory standard will play a significant part in next-generation EPYC processors.

EPYC’s on-board HBM hybrid design can be leveraged to boost IPC while maintaining the same core count. Tom also anticipates Zen 5-based EPYC server goods to be among the first AMD EPYC server products to integrate HBM designs, with EPYC Venice standardising it across many SKUs.

Finally, while all of this sounds fantastic, keep in mind that we’re talking about items that will be released in 3-4 years, and a lot may happen in that time. However, it appears that AMD’s EPYC Venice will be a reality.

also read:

Apple reports a whopping near-to $100 billion in revenue this year, and the year isn’t over yet