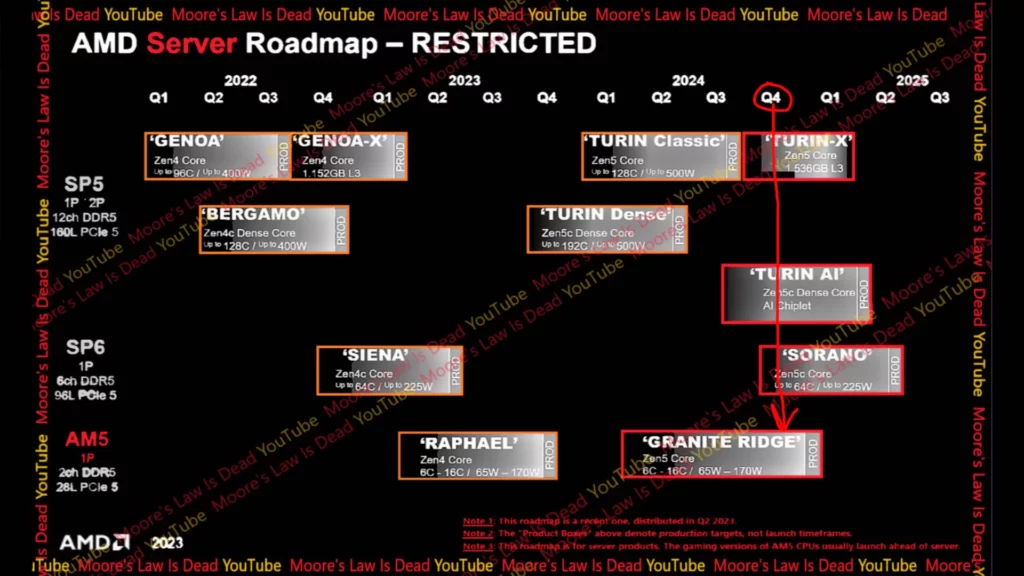

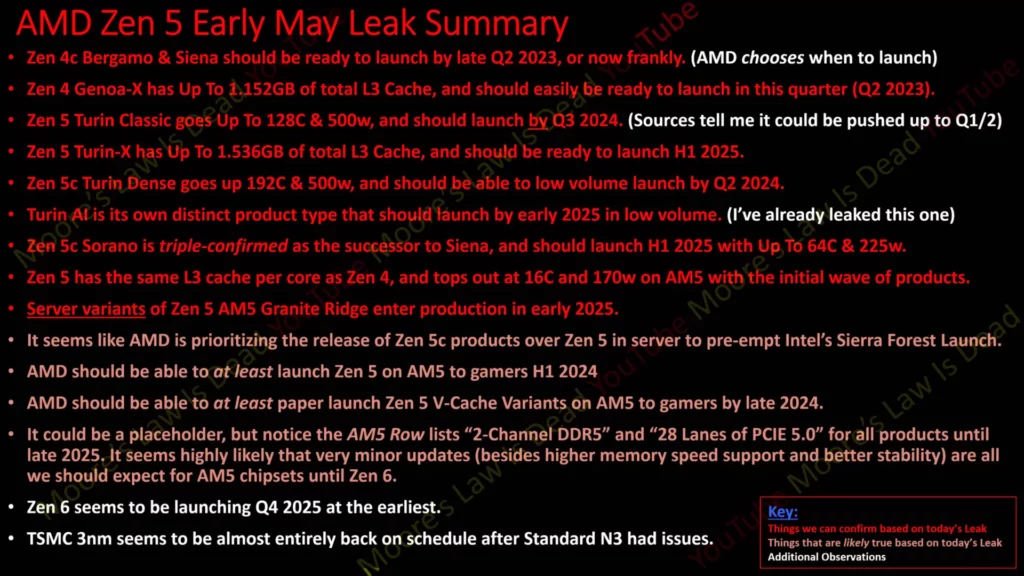

In addition to the leaked details about the Ryzen 8000 series, further information has emerged regarding AMD’s upcoming EPYC Turin CPUs powered by Zen 5 and Zen 5C architectures. These revelations come from the latest roadmap by Moore’s Law is Dead, providing insights into the expected next-generation EPYC CPU families set to debut between 2024 and 2025. AMD has officially confirmed Turin as its forthcoming EPYC family, leveraging both Zen 5 and Zen 5C cores.

Let’s delve into the specifics. The initial focus lies on the AMD EPYC Turin (Classic) family, which will retain the chiplet design and accommodate up to 128 cores, 256 threads, and configurable TDPs up to 500W (possibly even reaching 600W for certain SKUs, as revealed in a recent Gigabyte leak). Prior leaks indicated that the EPYC Turin chips would incorporate the same L2 and L3 cache as Zen 4, albeit with a minor enhancement to the L1 cache.

However, the most notable change arrives in how AMD organizes the cache on Zen 5 chips, expected to adopt a “Ladder” hierarchy. These chips are projected to enter production by Q1 2024, utilizing TSMC’s 4nm process node, and an actual launch is anticipated in Q3 2024.

Moving forward, let’s discuss the AMD EPYC Turin-X chips, which will integrate 3D V-Cache technology. These chips will retain 64MB of 3D V-Cache per CCD, totaling 1024MB across 16 CCDs, in addition to 512MB of standard L3 cache. This accumulation results in a grand total of 1536MB or 1.5GB of L3 cache.

When combined with the 1MB L2 cache per core or 128MB in total, the overall cache expands to 1664MB, not considering the L1 cache. This represents a remarkable 33% increase in cache compared to the upcoming Genoa-X CPU family.

We encounter the AMD EPYC Turin Dense chips, presumed successors to the Bergamo series.

Although Turin Dense is not the official name at this point, these chips are expected to employ 3nm Zen 5C cores in SKUs with up to 192 cores. TDPs of up to 500W are projected, but what’s particularly intriguing is that these chips are anticipated to enter production ahead of the standard Turin chips. This accelerated timeline likely stems from AMD’s aim to directly compete with Intel’s Sierra Forest 144-core chips, also expected in the first half of 2024.

Additionally, there is a secondary Turin Dense chip known as Turin AI. This variant is expected to feature the same Zen 5C cores, but accompanied by an AI chiplet. While specific details remain limited, it is anticipated that Xilinx IP will power the AI chiplet for specialized applications. Given AMD’s prioritization of AI as a strategic objective, incorporating AI-specific hardware within EPYC CPUs aligns with the demands of customers.

Lastly, let’s touch upon the successor to AMD’s Siena CPUs, named Sorano. The AMD EPYC 8004 “Siena” lineup will employ Zen 4/4C cores on the SP6 platform, catering to mainstream, cost-effective, power-efficient deployments. These chips will support 6-channel memory and offer 96 PCIe Gen 5 interconnects. The EPYC 8004 lineup will encompass up to 64 cores with a TDP of 225W. Production is slated for the latter half of 2024, with availability expected sometime in 2025.

Also Read: