Semiconductor engineer Tom Wassick claims to have discovered 3D V-Cache functionality on one of AMD’s best GPUs, the RX 7900 XT. The engineer used infrared imaging to peer inside the 7900 XT’s die and discovered the same type of 3D V-Cache connection points found on AMD’s Zen 3 and Zen 4 architectures.

Wassick cannot say whether these TSV connection points will be used for caching, but AMD has no plans to expand its 3D packaging capabilities beyond vertically stacked cache at this time. This suggests that these connection points would be used with some sort of 3D cache in mind to improve gaming and/or compute performance.

3D V-Cache has been used successfully on AMD’s Ryzen and EPYC CPUs.

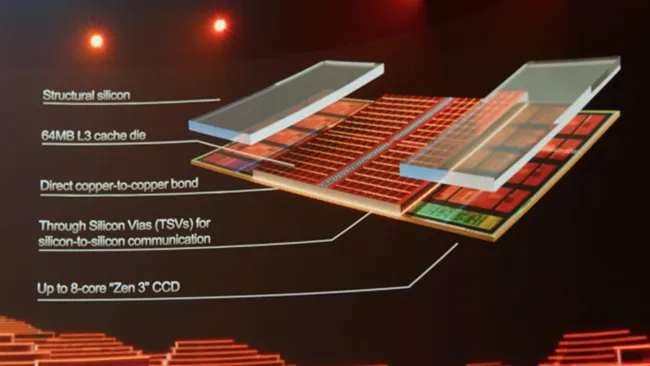

To increase L3 cache capacity, the technology employs a hybrid bonding technique that fuses an additional 64MB slab of cache on top of a Ryzen or EPYC compute die. This 3D stacking technique has currently enabled AMD to double the amount of L3 cache available on its desktop Ryzen 9 7900X3D and 7950X3D parts while tripling it on its Ryzen 7 5800X3D, 7800X3D consumer chips, and EPYC Milan-X server processors.

The performance gains from this technology have been impressive, with 3D-V-Cache chips gaining a full generational increase in performance in applications that heavily rely on large chunks of cache. A good example of this is the Ryzen 7 5800X3D, which had a 28% improvement in gaming performance over the Ryzen 9 5900X and was 7% faster than the Core i9-12900KS.

AMD’s server counterparts are even more impressive, with Milan-X benchmarks from AMD and Microsoft revealing performance gains of more than 50% over standard Milan parts. This technology, however, cannot magically boost performance at will. Only workloads that are cache-sensitive will exhibit this behaviour.

Also Read: