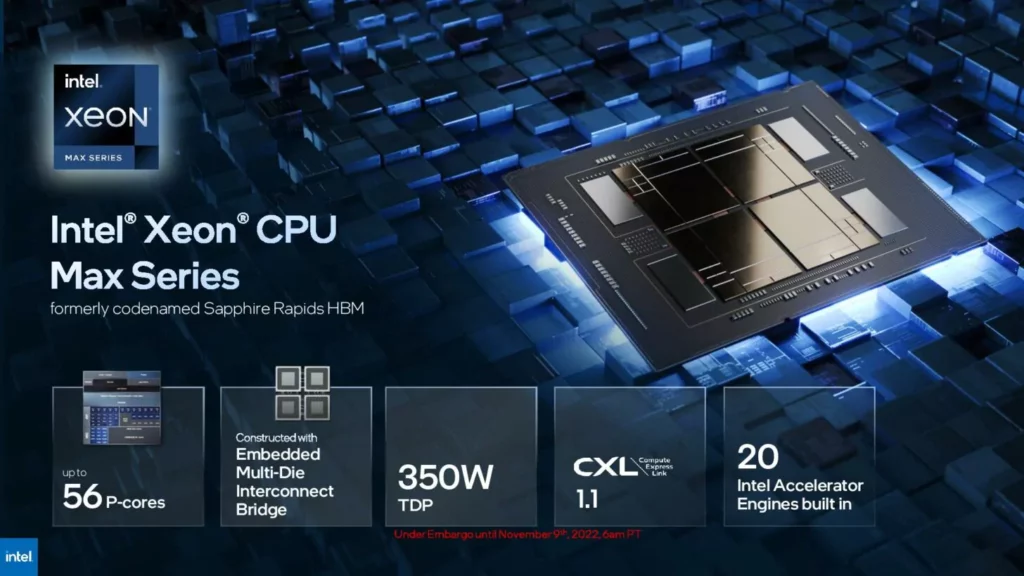

Recently, Intel unveiled its Xeon Max “Sapphire Rapids” CPU family with HBM2e memory. We now have a first look at the specifications and costs of the CPU family, even though Intel gives a technical disclosure with performance estimates and technological details of the lineup. The most recent leak originates from Yuuki AnS, who lists at least five Intel Xeon Max CPUs from the Sapphire Rapids HBM lineup in a subsequent post.

Only the bare minimum of information, including model names, core counts, core clocks, and pricing, has been disclosed by the leaker. The TDPs, Power Limits, Boost clocks, and cache configurations, among others, have not yet been disclosed. However, based on the specifications, it appears that Intel is relying solely on HBM2e memory for increased performance rather than the clocks, much like AMD does with its 3D V-Cache components. These make sense because they were created specifically for workloads that maximize bandwidth and cache. These chips’ core counts and cache are comparable to those of the non-HBM2e lineup.

When comparing prices, Intel’s HBM2e Sapphire Rapids Max CPUs are significantly more expensive than AMD’s EPYC Genoa components.

The most expensive AMD EPYC Genoa processor, which has 96 cores, has an MSRP of $11,805 US. While this is going on, Intel is charging roughly $13K US for a 56-core model and $11.5K US for a 52-core model with 64 GB of HBM2e memory. The performance needs to be superior to AMD’s EPYC Genoa for this pricing, which is pretty high, to be justified.

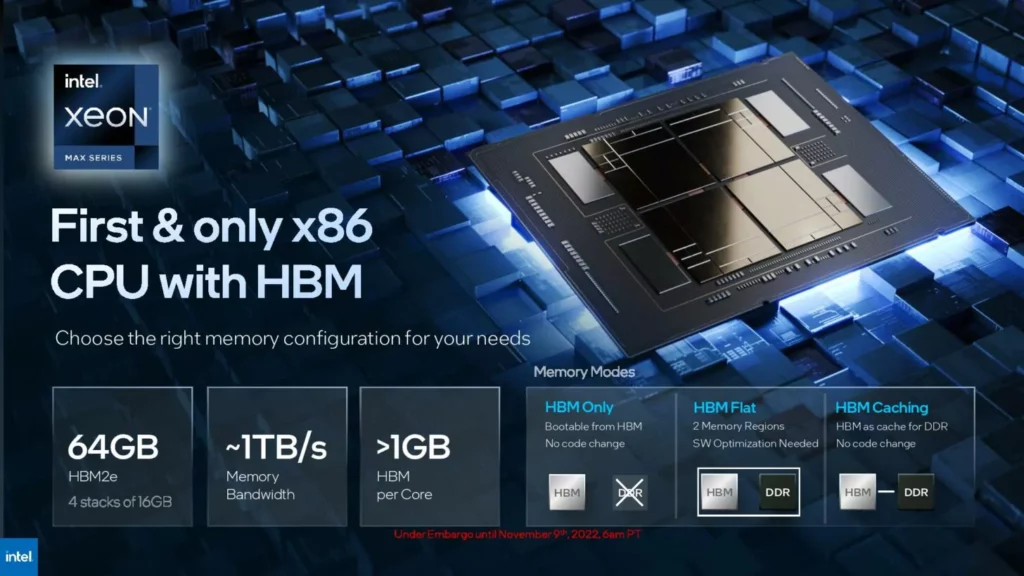

The Sapphire Rapids Xeon Max CPUs from Intel with HBM memory have also been described. According to what Intel has demonstrated, its Xeon CPUs will support up to four HBM packages, each of which offers much more DRAM bandwidth than a standard Sapphire Rapids-SP Xeon CPU with eight channels of DDR5 memory. This will enable Intel to provide clients that require it with a chip that has both greater capacity and bandwidth. There are two ways to use the HBM SKUs: flat mode and caching mode.

Ten EMIB interconnects will be present on the basic Sapphire Rapids-SP Xeon CPU, which has a massive 4446mm2 total package size. As we switch to the HBM version, the number of interconnects rises to 14, which are required to link the HBM2E memory to the cores.

Also read: